突破2nm极限:高NA EUV引领下一代芯片革命

- 2025-07-29 08:00:00

引言

随着摩尔定律逼近物理极限,半导体制造对更高分辨率与更精细图形化能力的需求日益迫切。EUV(极紫外)光刻作为先进节点的核心技术,正通过数值孔径(NA)的提升不断突破工艺瓶颈。ASML推出的高NA EUV(0.55NA)平台,是继0.33NA EUV之后的又一关键里程碑,不仅在分辨率、叠加精度和产能上实现显著跃升,也为2nm及以下制程的量产奠定了坚实基础。本报告将系统解析高NA EUV的技术原理、生态构建、整机集成进展、性能验证及未来发展方向,以呈现这一技术在半导体产业链中的战略价值与前景。

原报告我放在了知识星球

一、EUV技术与产品路线图

过去35年,光刻分辨率实现了近两个数量级的提升,这一进程主要通过波长缩短、数值孔径(NA)提升以及照明条件(k1因子)优化协同推动。ArF(193nm)光刻及其沉浸式技术(ArF Immersion)为当前先进制程奠定了基础,但随着摩尔定律推进,EUV(极紫外)光刻成为行业突破的关键。

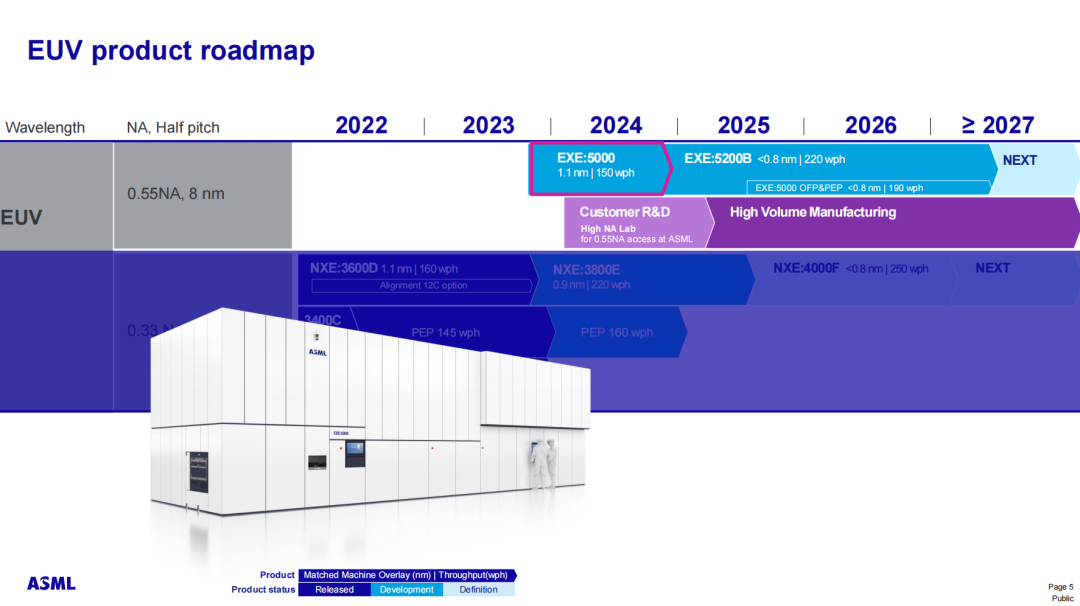

EUV采用13.5nm波长光源,其代表性设备包括0.33NA和0.55NA两大技术平台。0.33NA EUV(NXE系列)已进入高产能量产阶段,主要机型包括:

NXE:3400系列:3400B(1.5nm分辨率,112wph)和3400C(1.5nm分辨率,135wph);

NXE:3600D:分辨率1.1nm,产能160wph,并引入12C对准选项;

NXE:3800E:分辨率0.9nm,产能220wph;

NXE:4000F:分辨率<0.8nm,产能250wph。

随着制程节点向2nm及以下演进,高NA EUV(0.55NA平台)成为关键发展方向。ASML的EXE系列设备路线包括:

EXE:5000:分辨率1.1nm,产能150wph;

EXE:5000 OFP&PEP:分辨率<0.8nm,产能190wph;

EXE:5200B:分辨率<0.8nm,产能220wph。

整体来看,EUV技术路线的核心目标是进一步提升分辨率与产能,同时确保匹配机台的叠加精度(Matched Machine Overlay)稳定在亚纳米级别,以支撑先进逻辑与存储工艺的量产需求。ASML还计划通过高NA实验室(High NA Lab)为客户提供0.55NA平台的早期验证与工艺开发支持。

二、高NA EUV技术原理与创新

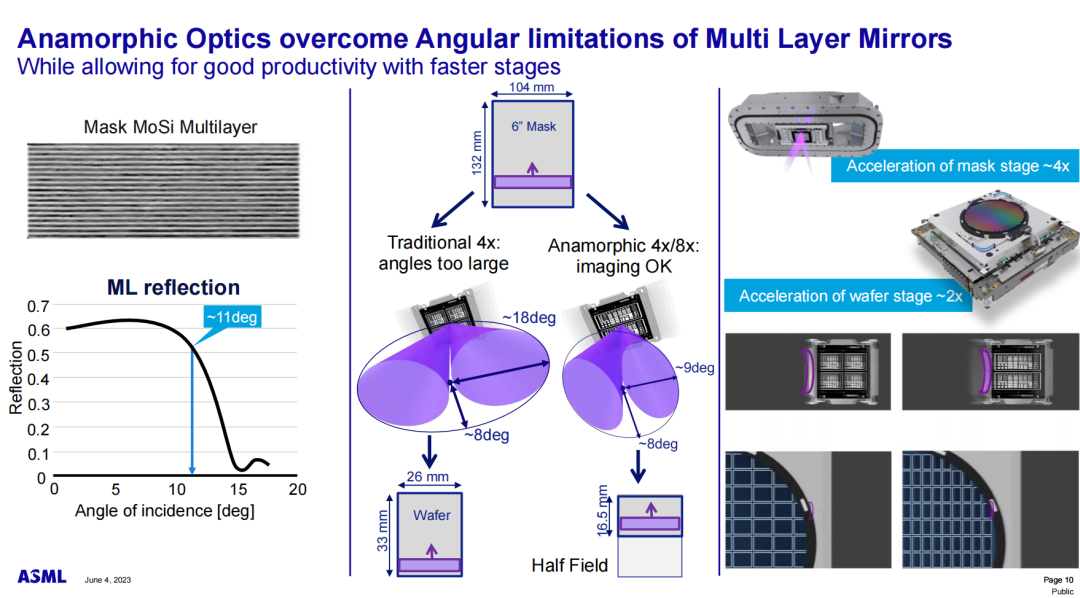

高NA EUV的核心在于通过更高数值孔径(0.55NA)实现更高分辨率,从而推动2nm及以下先进节点的量产。其技术基础源于13.5nm波长的EUV光学系统。在该波段,折射率接近1,且材料不可避免存在吸收特性,因此采用多层膜(MoSi multilayer)反射镜来实现高效的布拉格反射。反射率具有明显的角度依赖性,需在光学设计中严格控制入射角。

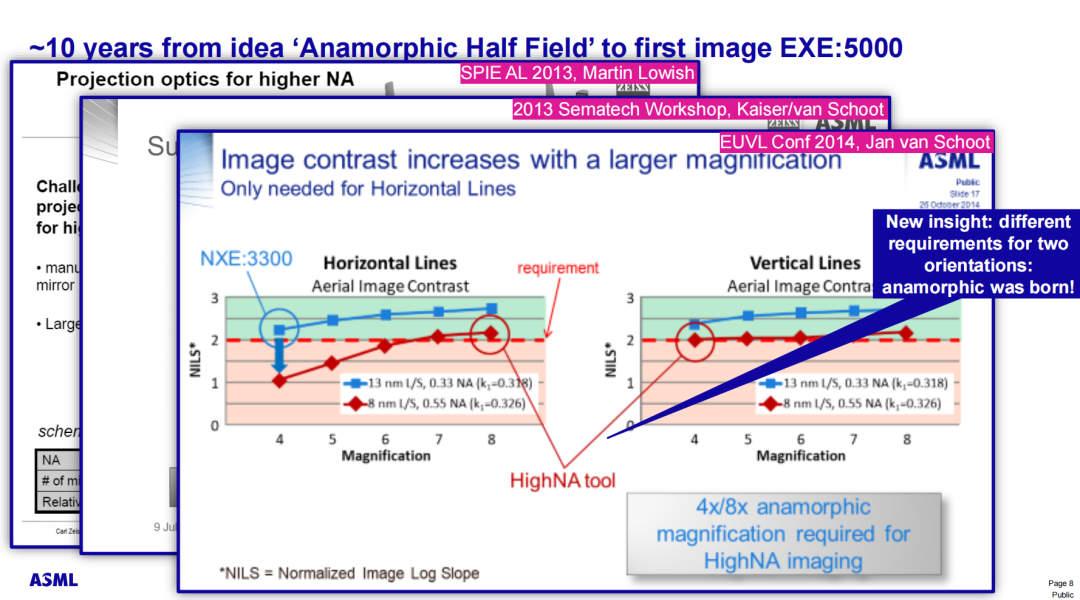

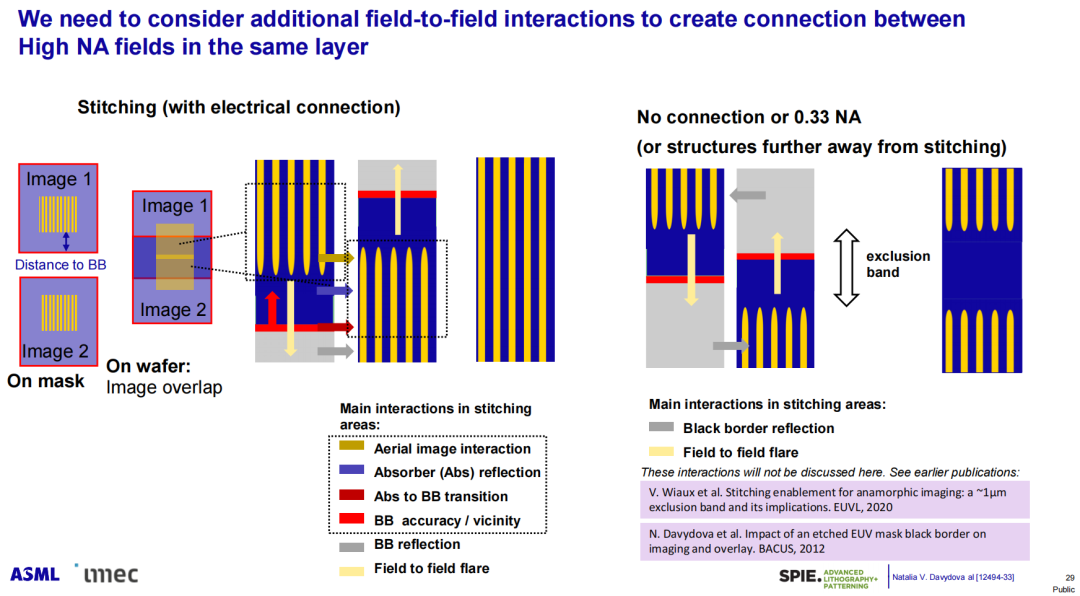

非等距(Anamorphic)成像 是高NA EUV的一大创新。传统4x放大在高NA下会导致过大的入射角,增加反射损耗与像差。而Anamorphic方案采用X方向8x、Y方向4x的非等距放大模式,将曝光场缩减为半场(Half Field),既能保持成像质量,又提升了扫描速度(掩模台加速度约为传统的4倍,晶圆台加速度约为2倍)。为了实现完整芯片图案,高NA EUV需采用拼接(Stitching) 技术,该方案在NXE平台上已验证拼接误差低于1nm,满足先进逻辑器件的叠加精度要求。

光学组件创新 是提升成像性能的另一关键。高NA EUV的投影光学盒(Projection Optics Box, POB)及照明模块需在极小的反射损失下传递高分辨率图像。系统采用分区模块化设计,允许单独更换镜片与照明模块,以便快速维护和产线恢复。同时,光源与0.33NA EUV具有高度共性,仅在结构方向上做出优化,以支持更高的功率和稳定性。

此外,高NA EUV对掩模(Mask)与光刻胶(Resist)提出了更严苛的要求。低n掩模可带来更高成像对比度,但对吸收层高度与CD偏差的敏感性提升2-3倍。为解决M3D效应与像差问题,需要更精准的光学邻近校正(OPC)与自由曲线设计策略。同时,在16nm及以下半间距测试中,高NA工艺表现出28%的LCDU改善,相较0.33NA有显著优势。

高NA EUV技术通过光学创新、非等距成像、模块化设计以及材料和工艺优化,突破了0.33NA的物理限制,为未来的2nm及以下制程提供了新的光刻解决方案。

三、高NA EUV生态系统与产业链

高NA EUV生态系统的构建以最大化与0.33NA EUV的共性为目标,旨在降低技术引入风险并加速平台成熟度。在八个主要模块中,有五个与0.33NA保持共用,包括光源容器、驱动激光器、晶圆传输模块、投影光学与照明模块以及掩模传输模块。这种高度共性化的架构不仅提升了服务与维护的便利性,也确保了高NA EUV的可制造性与量产准备度。

客户采用与市场布局

当前所有0.33NA EUV的主要客户均已公开宣布将引入高NA EUV设备。

台积电(TSMC):计划于2024年引入高NA EUV扫描机,建设配套的基础设施和图形化解决方案以满足客户需求。

英特尔(Intel):明确将高NA EUV作为延续摩尔定律的关键技术,通过与ASML的紧密合作,推动其制程向更小几何节点演进。

三星电子与SK海力士:已订购高NA EUV设备,主要应用于2nm逻辑制程和新一代平面DRAM工艺。

供应链与模块化生态

高NA EUV的设计强调服务性和可维护性。掩模台可在不拆卸其他部件的情况下单独移除,水路和模块化接口的优化显著缩短了维护与热稳定恢复时间。投影光学盒(POB)与照明模块的镜片均可独立更换,以确保快速恢复生产。ASML在Wilton、Veldhoven、San Diego与Oberkochen四地的工厂联合推进光源、掩模、晶圆和光学主模块的集成,以支持EXE:5000和EXE:5200系列的批量化交付。

光罩与材料技术

高NA EUV的掩模材料与制造工艺需满足更高的对比度与更小的误差容忍度。低n吸收层掩模在反射率与成像对比度上具有显著优势,但对掩模厚度控制与线宽偏差的要求更为严格,容差缩小至0.33NA掩模的1/2至1/3。同时,黑边(Black Border)反射和场间光晕(Field-to-Field Flare)成为关键挑战,需要光罩厂商、OPC/RET算法提供商以及扫描机厂商的深度协同。

光刻胶与工艺支持

为适配高NA的成像特性,光刻胶(Resist)和工艺开发也在同步优化。实验验证显示,在16nm半间距下,采用高NA类参数的LCDU改善约28%,显著提升了临界尺寸的均匀性。这一成果为2nm及以下节点的工艺窗口提供了更多弹性。

整体来看,高NA EUV生态系统已初步成型,涵盖设备制造商、光罩供应商、材料厂商与晶圆厂的紧密合作。通过模块化、共性化和早期验证平台(如High NA Lab)的联动,高NA EUV的商业化落地将加速整个半导体产业链的迭代与升级。

四、高NA EUV整机集成与制造进展

高NA EUV整机集成工作正在ASML的全球制造与研发基地同步推进,包括荷兰Veldhoven、美国Wilton、San Diego以及德国Oberkochen。整机由四大核心主模块——晶圆(Wafer)、掩模(Reticle)、光源(Source)和光学(Optics)——组成,各模块均已完成关键技术验证并进入批量化组装阶段。

1. 光源模块(Source)进展

三套EXE:5000光源主模块已在ASML完成全面验证,功率指标达到量产要求。EXE:5200原型光源的目标功率超过360W,并已实现超过1000亿次脉冲的稳定运行,锡(Sn)管理与光源寿命测试均达到设计规范。0.55NA光源与0.33NA平台具备高度共性,但在光源朝向和能量稳定性方面进行了专项优化。

2. 晶圆模块(Wafer)与晶圆台

四套晶圆主模块已完成组装与伺服控制验证,晶圆台运动精度和速度均达到<0.8nm叠加误差要求。晶圆传输与台面系统的优化显著缩短了恢复时间并提高了生产稳定性。该模块的多套原型机正用于高NA技术的成熟度验证。

3. 掩模模块(Reticle)

掩模主模块及其传输系统已在ASML Wilton工厂完成搭建与测试。掩模台可在无需拆卸其他部件的情况下独立移除,提升了服务效率与热稳定恢复能力。掩模传输系统完成了长周期运行验证,确保了高精度掩模的搬运与对准性能。

4. 光学模块(Optics)与投影系统

投影光学盒(POB)和照明模块的核心镜片已经完成设计与镀膜,所有高NA光学镜片的波前、透过率和散射指标均符合设计要求。光学模块的安装和调试正同步推进,并为多台客户设备提供量产镜片。

5. 系统级集成与调试

Veldhoven(晶圆模块):晶圆主模块集成和伺服控制调试正在进行。

Wilton(掩模模块):掩模台和传输系统已完成组装与循环验证。

Oberkochen(光学模块):镜片生产与POB组装正在持续加速,满足多客户需求。

San Diego(光源模块):高功率光源实现批量生产能力。

6. EXE:5000整机建设

首台EXE:5000整机已完成四大主模块的安装与调试,进入高NA实验室(High NA Lab)阶段。该实验室计划在2024年正式为客户和供应商开放,用于早期工艺开发和高NA曝光验证。

整体来看,高NA EUV整机集成取得显著进展,模块化架构与跨区域协同确保了系统按计划推进,为2024年高NA EUV的产业化和客户导入奠定了坚实基础。

五、关键性能指标与验证数据

高NA EUV在关键性能指标方面已取得多项验证成果,显示出显著的分辨率和均匀性提升,为先进制程的量产提供了强有力的技术保障。

1. 分辨率与图形质量

通过0.5NA MET5平台的实验验证,高NA EUV在16nm半间距图形下展现出卓越的成像能力。与0.33NA参数相比,高NA类设置使临界尺寸(CD)由15.8nm略降至15.6nm,同时分辨率的细节保真度更高,能够满足更先进逻辑与存储节点对线宽控制的严苛要求。

2. LCDU与均匀性改善

在16nm半间距条件下,采用高NA类曝光参数可将线宽均匀性(LCDU)从4.36nm降低至3.15nm,改善幅度达到28%。该结果表明,高NA EUV在提升图形一致性和减少随机线宽波动方面表现出明显优势。

3. 缺陷控制

在扫描电子显微镜(SEM)视野下,缺陷数量由0.33NA模式下的7个显著减少至高NA模式下的0个。这一数据说明,高NA工艺的图形质量和缺陷率控制有了质的提升,有助于提高整体良率。

4. 光源功率与产能指标

EXE:5000系列设备的目标分辨率达到1.1nm,产能150wph;EXE:5200B的分辨率进一步提升至<0.8nm,产能达到220wph。与之对应的NXE:3800E和NXE:4000F机型也在分辨率和吞吐率上不断刷新纪录,其中NXE:4000F可实现<0.8nm分辨率和250wph的产能。

5. 拼接与叠加精度

高NA EUV采用半场(Half Field)曝光策略,需通过拼接(Stitching)实现完整图案。相关实验结果显示,其拼接误差控制在1nm以内,满足亚纳米级叠加(Overlay)要求,为2nm及以下制程节点提供工艺保证。

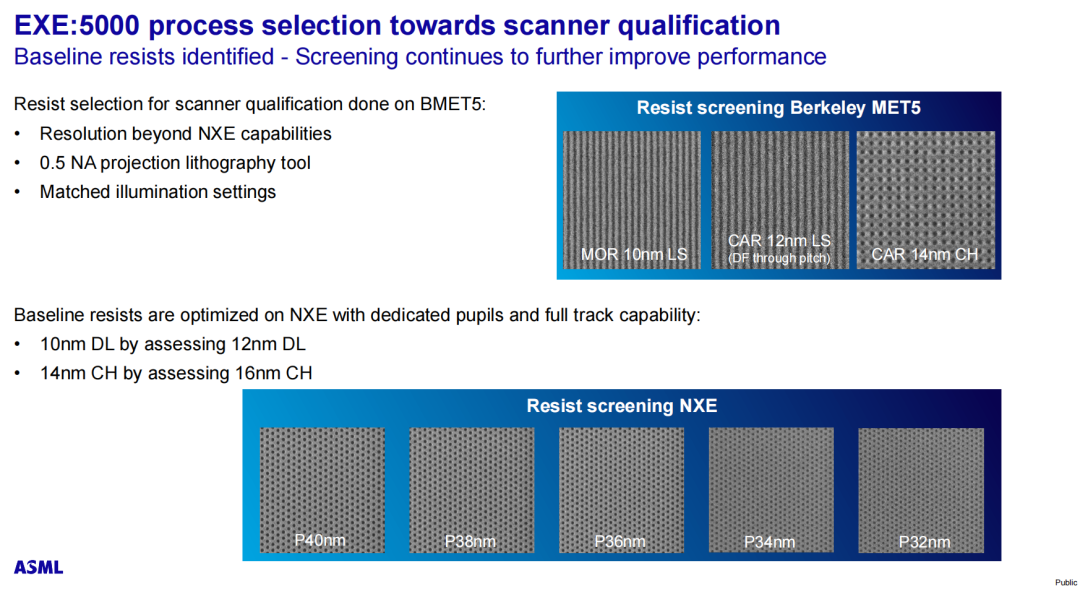

6. 光刻胶与材料适配性

基于Berkeley MET5平台的光刻胶筛选和优化工作表明,基础光刻胶已具备满足10nm线间距和14nm接触孔的成像能力。配合0.55NA照明条件,进一步优化了光刻胶的解析度与缺陷控制。

整体来看,这些关键指标验证了高NA EUV在分辨率、产能、叠加精度和缺陷控制方面的综合优势,进一步巩固了其在2nm及以下制程中的核心地位。

六、未来技术挑战与发展方向

高NA EUV的成功量产不仅依赖当前0.55NA平台的成熟度,还需解决未来节点所面临的多重技术挑战,并探索更高NA及延伸工艺方案。

1. 持续提升成像质量与生产效率

在保证高分辨率和高对比度的同时,高NA EUV需持续优化生产效率。除了保持生产率(WPH)和叠加精度,系统还需进一步降低随机光刻误差和颗粒缺陷,从而实现大规模稳定量产。

2. M3D效应与随机性问题

随着节点缩小,多层结构(M3D)效应和随机性(Stochastics)对成像质量的影响日益显著。为此,ASML提出通过优化照明、掩模结构和光刻胶特性等手段,减缓M3D造成的图形失真,确保线宽控制的稳定性。

3. 掩模与低n材料的迭代

低n吸收层掩模(Low-n mask)已成为高NA EUV的关键组成,但其制造精度要求远高于0.33NA掩模。掩模对吸收层高度、CD偏差和黑边(Black Border)反射的敏感性显著增强,需要与OPC/RET算法和掩模厂商深度协同,确保在场边拼接和光晕控制上的一致性。

4. 光刻胶(Resist)及工艺窗口拓展

传统化学放大量子光刻胶(CAR)在分辨率与缺陷控制方面接近极限。金属氧化物光刻胶(MOR)因其更高的光敏性能与低缺陷率,正在成为未来关键材料。高NA曝光条件下的光刻胶筛选与优化需与NXE、MET5等平台同步推进,以确保10nm及以下线间距和接触孔的可量产性。

5. 照明与光学结构优化

高NA EUV正探索高透过率与高灵活性的照明系统,通过减少镜片数量来提升光传输效率,并利用更灵活的瞳孔填充率(Pupil Fill Ratio >10%-20%)实现低k1成像。在此基础上,更高NA(>0.75NA,Hyper NA)光学平台的研究已启动,目标是实现更高分辨率与更广工艺窗口。

6. EUV技术的延伸路线图

未来EUV产品将基于共性化平台策略,向更高传输率、更高分辨率的方向演进。随着0.55NA平台稳定量产,ASML与合作伙伴正研究Hyper NA方案及进一步优化自由曲线OPC、强偏置(Strong Bias)和相移掩模(PSM)等技术,以支撑2030年后的1nm级节点。

综上,高NA EUV不仅是当前制程的关键突破口,更是未来工艺演进的技术基石。其在掩模材料、光刻胶、光学系统和照明结构上的持续创新,将决定摩尔定律在亚纳米时代能否延续。

来源:半导体产业报告

芯启未来,智创生态

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊