人均年薪53万!芯片行业哪个岗位工资最多?

- 2025-07-28 08:25:00

芯片最赚钱的岗位居然是数字前端的设计验证工程师,真是不可思议!人均年薪高达53.45万元!

以下数据来自猎聘网的调研报告。

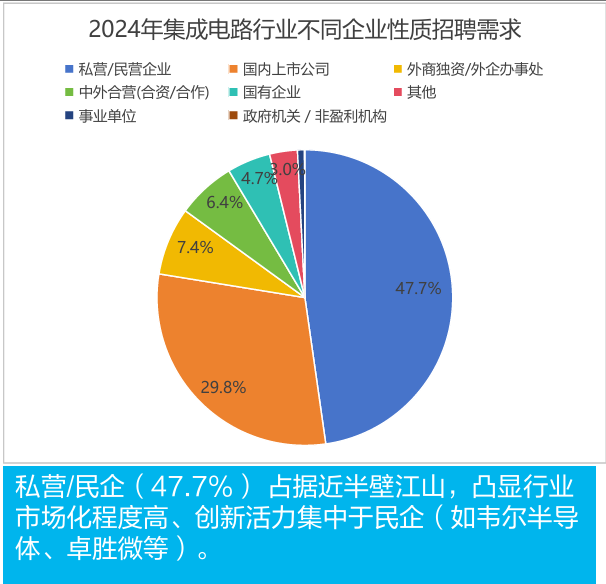

在集成电路行业,那到底哪个类型的企业招聘需求更多呢?私企还是国企?大企业还是小企业呢?

芯片设计方向:技术与工具的深度耦合

1. 数字IC设计

核心技能技能其实主要就以下几个方面:

(前端)精通Verilog/VHDL硬件描述语言,掌握SystemVerilog验证方法学

(后端)熟悉数字前端全流程(RTL→综合→形式验证→时序分析),熟练使用DC、Formality、PrimeTime工具

(前端以及架构)深入理解处理器架构(如RISC-V、ARM Cortex)和总线协议(AXI/APB/OCP)

(设计、后端、系统等)掌握UPF低功耗设计流程,在40nm以下工艺实现时钟门控、电源隔离

比如要设计28nm移动处理器时,需使用ARM或者RISCV或者X86等CPU核的IP,当然自己开发也可以,再通过熟悉接口做好各类外设的接口控制逻辑,就是第一个技能,熟练掌握Verilog等语言,然后就是验证相关的,到中后端,使用DC工具完成综合,使用Innovus或者ICC2等EDA工具完成布局布线等,控制插入延迟偏差<30ps,并采用多重电压域设计降低动态功耗23%等,所以工具与技能都要熟练掌握。

2. 模拟/混合信号IC设计

掌握关键技能点能力如下:

器件知识:晶体管级电路设计能力(CMOS、Bipolar、FinFET器件物理特性掌握)

各种参数控制:高频电路参数控制技巧(例如LDO的PSRR>80dB@1MHz)

复杂模拟电路模块开发经验:(PLL时钟抖动<100fs,ADC实现ENOB>14bit等)

熟练操作Spectre、HSPICE仿真工具,具备Monte Carlo分析能力

制造工艺方向:精度与稳定性的平衡艺术

1. 半导体工艺开发

基本的一些技术要求:

精通光刻工艺(DUV到EUV光刻机台操作,套刻误差控制<2nm)

掌握薄膜沉积技术(ALD制备高k介质时厚度波动<1Å)

等离子体刻蚀工艺优化能力(深宽比50:1的TSV刻蚀均匀性管控)

良率提升方法论(SPC控制Cpk>1.67,解决defect密度<0.05/cm²)

比如工艺相关的项目可以是:在3D NAND制造中,工程师需建立96层堆叠的阶梯刻蚀工艺,通过脉冲式刻蚀与原子层沉积交替,将层间厚度偏差控制在±1.5%以内。

2. 器件整合工程

必备基本能力:

FinFET/GAA纳米片结构的TCAD模拟能力

应力工程技术(SiGe源漏应变提升电子迁移率30%)

可靠性验证技能(HCI寿命预测模型误差<10%)

掌握TEM/FIB等微观分析设备操作

比如如下的项目:随着环栅晶体管(GAA)量产,工程师需要建立原子层掺杂(ALD doping)工艺,在1nm节点实现阈值电压±20mV波动控制。

封装测试方向:系统级集成的技术突破

1. 先进封装技术

核心能力:

2.5D/3D封装设计能力(硅中介层布线密度>10k/mm²)

微凸点工艺开发(5μm直径铜柱共晶焊接技术)

热应力仿真优化(通过ANSYS Icepak实现芯片结温<125℃)

掌握TSV深孔填充工艺(高深宽比50:1的铜电镀技术)

比如以下项目:在Chiplet异构集成中,工程师需解决不同工艺节点芯片的热膨胀系数匹配,采用有机中介层将CTE差异控制在1ppm/K以内。

2. 测试工程开发

基本技能要点:

- ATE测试程序开发(Teradyne UltraFLEX平台脚本编写)

- 高速接口测试技术(PCIe 5.0眼图模板达标率>99.7%)

- 大数据分析能力(通过1E6个测试数据点建立多维良率预测模型)

- 掌握SLT系统级测试方案(全功能场景覆盖测试>85%)

比如以下项目:5G基带芯片测试需开发毫米波OTA测试系统,在28GHz频段实现±0.5dB功率测量精度,同时将测试时间压缩至传统方案的30%。

EDA与IP开发方向:产业链的赋能基石

1. EDA工具开发

基本核心技术:

- 数学建模能力(发展时序签核的统计静态时序分析算法)

- 并行计算优化(实现布局布线工具的多核加速比>32x)

- 机器学习应用(利用GAN网络生成布线模式库)

- 物理验证引擎开发(DRC规则检查速度突破1M layers/hour)

典型项目案例:开发7nm以下工艺的签核工具时,需建立新型漏电模型,将电流密度计算误差从传统BSIM模型的15%降至3%以内。

2. IP核开发

主要基本能力:

- 标准接口协议实现(DDR5 PHY满足6400Mbps速率)

- 工艺移植能力(28nm到12nm的IP移植性能提升验证)

- 安全防护技术(PUF物理不可克隆函数实现>98%唯一性)

- 低功耗设计技巧(物联网IP静态功耗<10nW/MHz)

EETOP 创芯大讲堂 数字IC前端设计课程推荐

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊