AI需求飙升!ASML新光刻机直击2nm芯片制造,尼康新品获重大突破

- 2025-07-24 07:00:00

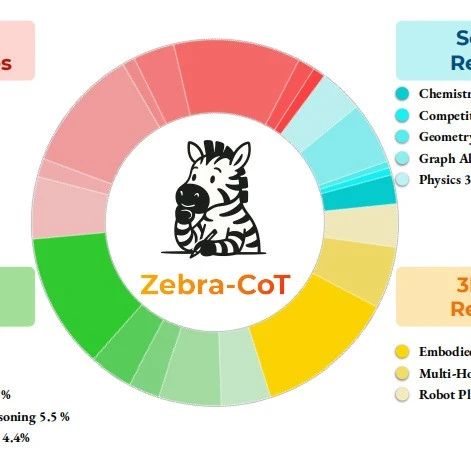

AI芯片需求旺带动先进封装需求,FOPLP技术获得青睐

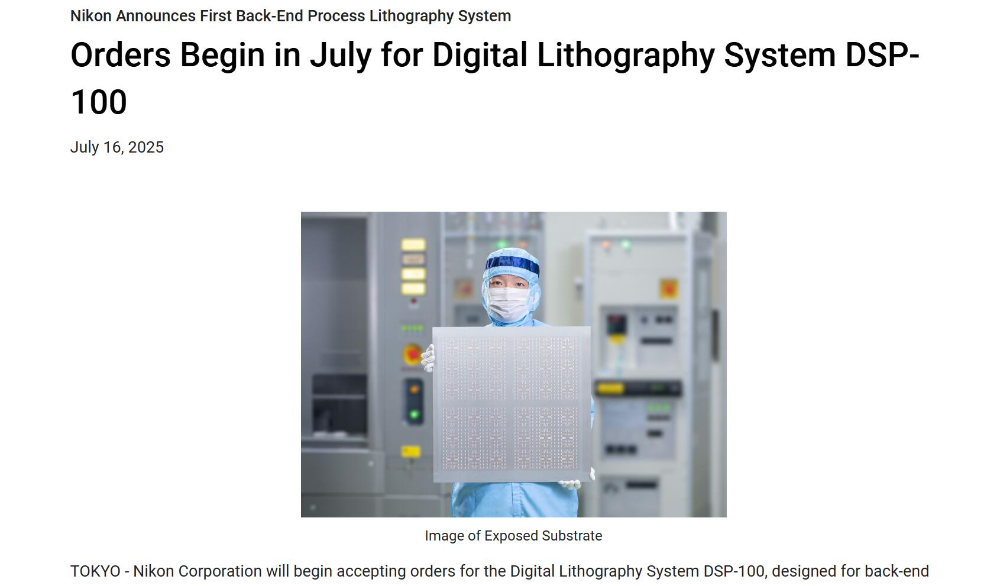

基板制造效率提升9倍!DSP-100横空出世,给晶圆代工厂商带来重大利好

ASML宣布:全球首台第二代High NA EUV出货,剑指2nm先进制程

写在最后

更多热点文章阅读

点击关注 星标我们

喜欢就奖励一个“在看”吧!

喜欢就奖励一个“在看”吧!

声明:本文内容及配图由入驻作者撰写或合作网站授权转载。文章观点仅代表作者本人,不代表科技区角网立场。仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

点击这里

扫码添加微信

扫码添加微信

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊