免费分享技术视频+PDF资料:Arteris 专为SoC集成打造的Magillem Connectivity工具

- 2025-07-30 08:20:00

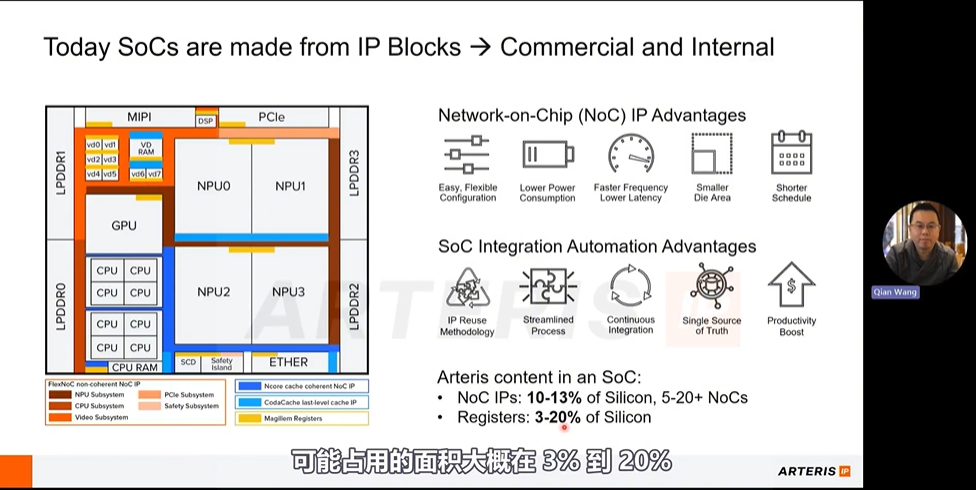

摩尔定律正在逐渐放缓。随着半导体行业(尤其是受AI算力需求的驱动)加速提升性能与能效,基于multi-die系统的架构创新变得至关重要。近日,Arteris推出专为互操作性打造的升级版Multi-Die解决方案。该方案支持通用芯粒互连标准(UCIe)、多种Arm AMBA协议、PCIe,并能与主流物理IP集成,从而确保基于行业标准的强健生态系统兼容性。

Arteris Multi-Die解决方案的核心能力:

经过硅验证的非一致性FlexNoC IP支持相关行业标准,可与第三方商用晶粒间控制器及物理层接口(PHY)无缝集成。

新增缓存一致性Ncore NoC IP功能可实现跨芯粒的缓存一致性读写操作,使应用软件开发者能够将multi-die系统视为单一硅片进行操作。

优化的Magillem Connectivity自动化技术,支持从IP核与芯粒进行SoC组装,降低人工集成易出错带来的项目风险。

升级版MagillemRegisters自动化方案,基于单一数据源实现从系统映射定义到验证文档的软硬件协同集成。

技术创新的快速步伐以及对先进实体 AI 芯片日益增长的需求正在重塑 SoC 设计,从单片式架构转向基于芯粒的架构。

EETOP特邀Arteris为的资深技术专家大家分享Magillem Connectivity相关的技术培训课程,以及PDF资料文档,供大家快速且直观的了解Arteris的 Magillem Solution。

扫码获取视频及PDF资源

本期推荐视频,主题:

Magillem Connectivity for SoC Integration Automation

演讲人:王谦

Arteris 高级工程技术经理

电子工程硕士学位背景,在EDA领域拥有二十年的专业知识。他曾在顶尖的EDA公司担任过不同的EDA产品职位,并在领先的半导体公司担任过设计工程职位。

视频内容概要

Arteris 的 Magillem Solution 如何应对现代SoC 集成面临的挑战,以及集成工具Magillem Connectivity 的核心功能和特性。

产品技术白皮书

除以上视频课程之外,Arteris还为大家分享了两份白皮书:

资料一:Magillem Registers 软硬件接口自动化的统一方法

资料二:Magillem Connectivity完整的SoC集成解决方案

扫码获取视频及PDF资料

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊