从RISC-V嵌入式应用主场,一窥生态建设水平…

- 2025-07-23 17:17:02

今年RISC-V中国峰会相较往年的规模明显大了不少,这和RISC-V更广泛的应用有相当大的关系。比如下图中这款在消费市场相当有名的Insta360 Go3s运动相机,就在用全志F133芯片,搭载玄铁C906;还有拯救者游戏掌机,虽说AP SoC及图形加速并非基于RISC-V,但其中来自沁恒微的CH32V303,基于青稞RISC-V4F内核,用于其上手柄功能控制也相当重要...

更多日常生活中能见到的电子产品,都用上了RISC-V;下面这款键盘应当是狼蛛的F98pro

除了这两款,峰会展区内还有相当多认知度极高的电子产品,它们都和RISC-V接上了头——这放在5年前是完全不可想象的。而这些内部出现RISC-V痕迹的电子产品,也的确让人惊叹于RISC-V生态成长之迅速。

Omdia预计2030年RISC-V处理器的出货量会达到173亿颗,2024-2030的出货量CAGR 46%;从处理器出货量市场份额角度来看,Omdia预计2030年RISC-V的市场份额会达到24%。英富曼数据服务有限公司首席分析师许松在RISC-V中国峰会的嵌入式系统分论坛上说,“如果从IP核的角度来看,增长速度可以达到5-10倍”。

虽然如主峰会的报道中所说,RISC-V现阶段在HPC等高门槛、高附加值领域的市场份额依旧不大,但“RISC-V在消费、家电、可穿戴等嵌入式领域的发展已经非常出色;在控制等领域也展开了积极布局”。许松对于RISC-V应用的总结是,“RISC-V以其设计的灵活性和可扩展性,可应用于各个领域”,“向上发展可适应高计算密集场景,提供优异的能效比”,“向下则可以适配多样化的轻量级端侧应用,实现智能化升级”。

嵌入式系统分论坛的绝大部分参会者,主要还是围绕微控制器与物联网应用展开的讨论。芯原股份无线IP平台高级总监曾毅在演讲中说,到目前为止搭载RISC-V架构的嵌入式MCU出货量超过了10亿颗每年,“5年后这个数据应该会达到70亿颗/年”。因此,这称得上是RISC-V主场了,也是本届RISC-V中国峰会不少人说RISC-V“三分天下”的基本盘。那么本文就依托这场分论坛,看看RISC-V的主场发展成熟度达到了何种水平。

在物联网领域广泛应用的基础

我们在谈RISC-V于任何市场的应用时,都期望首先搞清楚该市场为何选择RISC-V:毕竟从商业市场角度看,技术自主化、地缘政治实则都顶多作为RISC-V进驻某个市场的“敲门砖”存在。如果它本身没有技术优势,那么最终都不会在市场上掀起多大的水花。

曾毅概括RISC-V在物联网领域广泛应用的原因主要在于其开源开放属性,带来的“多元化微架构实现”。(1)“RISC-V的多元化与可定制实现,在统一的指令集架构下能够实现多种规格的内核——这就为物联网碎片化和多样化的应用场景提供了充足的发挥空间。”

换句话说,“基于多层次可扩展的微架构,能够满足物联网应用的各种功能需求,从简单到复杂”,“最简单的比如时钟电源管理,安全处理或协议加速;稍微复杂一点的实时调度;更复杂的高性能任务管理、数据处理,乃至AI推理”,“都有不同规格的RISC-V内核可以满足需求。”毕竟芯原自己就在RISC-V相关的IP上给出了颇多解决方案。

(2)其次,可裁剪、可扩展的自由属性,还令RISC-V更易于去实践对芯片功耗与面积的优化,以及对成本的控制(包括指令集本身不需要授权费用对降低设计成本的价值)——这往往是嵌入式应用十分看重的;

(3)开放性还带来了社区合作,“共享开发工具链、共享软件生态资源”;

(4)对应的,这也带来了“同等级的安全与可靠性”......那么本文就循着这4点,来谈谈基于RISC-V的嵌入式应用。

当然RISC-V还有确保供应链安全、技术自主可控的优点等等。虽说面向不同应用场景时,我们可能会谈论RISC-V不同的价值,但说到底这些技术与市场相关的优势,都是其开放属性带来的。

芯思原研发总监高挺挺在谈RISC-V“助力大健康产品降本增效”时,给出了一份“某国产RISC-V核”与Arm Cortex-M3的对比,“分别从性能、面积、动态功耗三个维度”。虽然这份对比提供的信息量并不能算详实,但它能够体现的就是RISC-V格外适合“大健康”应用为代表的物联网芯片资源受限、追求低功耗与高能效的特点。

很容易想见,随着RISC-V生态的持续完善,更多嵌入式应用向RISC-V靠拢会成为常规。

“多样化应用场景”

虽然作为论坛报道,本文无法涵盖RISC-V在嵌入式应用之中优势的方方面面,不过我们依然可以选择一些角度来尝试解读上述属于RISC-V的优点,让各位读者更具体地感受RISC-V开放开源、可伸缩的价值。

依据上述曾毅总结的RISC-V在嵌入式领域的优势,首先要谈的自然是“多元化微架构实现”或者“多样化应用场景”。这一点实际并不需要多花笔墨,毕竟在RISC-V中国峰会的展区就能看到大量嵌入式应用都是基于RISC-V的。

这款游戏手柄同样采用沁恒微的低功耗蓝牙SoC芯片,基于青稞RISC-V内核

如果从嵌入式系统分论坛来看,那么大致可以举几个例子:首先是格见半导体介绍的用于替代TI C2000 DSP的GS32-DSP实时控制芯片,主要着眼在数字电源、数字能源、机器人、工业控制等电力电子领域——后文会谈到RISC-V在其中体现出的充沛价值。

单从市场应用角度来看,深圳格见半导体CEO陈文斌表示这系列产品就是围绕替代TI C2000而设计,做到了完全的Pin2Pin兼容,“主流型号100%覆盖”,“只比TI C2000最新型号晚6-12个月”,高性能型号“只有我们能规模量产”,且“和TI C2000软件平滑迁移”。据说格见的主力产品已经在行业头部客户量产导入100+家,可见RISC-V芯片产品在特定领域要挑战或替代市场巨头的高水平竞品,是完全行得通的。

另一个在现场演讲颇具代表性的企业是先楫半导体:这是一家将RISC-V芯片用到机器人身上的企业。电子工程专辑今年3月特别报道过这家企业的高算力MCU产品及其逻辑。先楫半导体产品总监及嵌入式专家费振东这次再度提及,先楫半导体的MCU遵循具身智能主控芯片的5大要求:(1)高算力;(2)高性能运动控制;(3)高实时性同步通讯;(4)高集成度与小型化;(5)高安全与高可靠性。

“在入门级、主流级MCU产品方面,国内有不少相当成功的厂商推出了很多不错的产品,但高性能、高算力方面还相对空白。”费振东表示。所以颇具代表性的、基于RISC-V,也是先楫在今年CES上发布的HPM6E8Y就成为了满足上述5个要求与趋势的热门产品:包括600MHz双核RISC-V,“首个国内获得正版授权,在运动控制应用广泛的EtherCAT从站控制器”,集成2x以太网百兆PHY、2MB SRAM、4MB Flash。

另据说先楫新推的HPM6750系列MCU已经做到了800MHz主频,“这在当时乃至现在,都是全球非常领先的高算力MCU”。先楫的产品体现的是RISC-V在高算力MCU以及机器人应用领域的价值。

再举个芯思原的例子:如前所述,芯思原在论坛上谈的主要是基于RISC-V、集成BLE的超低能耗MCU及其在大健康领域的应用。芯思原看到“大健康领域”的市场潜力巨大——据说今年中国大健康行业规模会突破15万亿,2028年预计突破20万亿。

所以针对现有大健康产品价格高、续航弱、实时传输能力弱,以及存在隐私安全风险几大挑战,芯思原在推的是RISC-V + BLE + 安全 + 超低功耗MCU。后文也会部分提到芯思原选择RISC-V的价值。

从上述这三个例子就不难发现,基于RISC-V指令集的芯片产品针对不同应用领域的不同痛点,是可以更具针对性地通过裁剪、扩展或定制,以相对更低的成本、更高的效率和性能,去契合特定市场需求的。

低功耗与高能效

有关RISC-V芯片的低功耗与高能效特点,恰巧在峰会主题演讲的圆桌环节,奕斯伟计算高级副总裁、首席技术官何宁谈到了一个例子:“我们之前遇到过基于某芯片产品,用纽扣电池的话能用上两年;我们在进入那块市场以后,就发挥了RISC-V极致可定制的优势,就能用上10年了。然后我们也以很快的速度取得了相当大的市场份额。”

另外,曾毅在分论坛上谈芯原的整合GNSS与BLE的基于RISC-V架构的SoC平台时,举例提及有客户“基于22nm FD-SOI工艺做了应用于安全无线摄像头的SoC芯片,基于RISC-V内核与无线连接技术”,据说凭藉两节AA电池,就能续航2年时间,“累计出货量超9000万颗”。除了芯原一直在宣传的“结合RISC-V优势与特点,用平台化方式缩短开发周期”,并藉由定制服务实现产品差异化,这自然是制造工艺配合设计,实践低功耗的典范了。

传说中两节5号电池用两年的智慧摄像头,基于芯原SiPaaS平台定制

这里再谈两个更具体的例子和实践。首先,基于RISC-V的可扩展性,可以带来特定负载效率大幅提升的例子。高挺挺在谈RISC-V的“用户可定制”属性时就提到,RISC-V支持模块化和指令扩展,“小到CRC计算,大到神经网络的卷积运算,都能通过指令扩展的方式实现。”

“以CRC为例,我们大致算了一下,以纯软件的方式去实现可能需要大约30个cycle;借助硬件挂到bus上实现,可能需要10个cycle;而如果用指令集去做,2个cycle就能完成,也就极大提升了计算效率”。

陈文斌则谈到格见的GS32-DSP芯片,基于芯来科技的RISC-V IP“深度定制”而来,“支持500+条RV32基础/扩展指令和适用于工业能源、电机等领域控制算法的深度定制指令,提供包括但不限于三角函数和数学运算单元(TMU)、电流环控制单元(CLU)等定制指令和典型算法函数库”。

“加上编译器的深度定制”,除了在诸多计算项目中,性能远超其对标的TI C2000之外,陈文斌表示,“三角函数(正弦&余弦)计算在电力电子领域是绕不过去的。用传统Arm架构(M7)去做,没有用上好的库,可能要400个cycle;用上非常好的库,我们实测也得80-100 cycles;而我们的产品只需要5个cycle”,“实时控制一般一个环路调10次,这样的计算就省掉1000个cycle——这是相当长的时延。”“这还只是基础指令集”,当涉及更复杂的DSA指令与计算,GS32-DSP还有更大的性能优势。

其次,在低功耗设计上颇有价值的一则信息是高挺挺特别去谈的芯思原SoC平台(主要是RISC-V MCU + BLE)低功耗架构设计,因为主题演讲中涉及的“大健康产品”需要具备长续航表现——无论是对健康的持续监测,还是提供长期可靠的趋势信息需求。他说“低功耗架构”要考虑的包括4个层级:系统级(system level)、架构级(architecture level)、设计级(RTL, design level)、器件级(transistor level)。

“系统级可以根据应用场景,去做一些partition;架构级,我们要去设计专用的PMU做全局功耗控制——也针对前面的partition做低功耗策略,如DVFS, power gating等;设计级的优化,比如尽量减少设计的冗余逻辑,毕竟这类应用无需考虑功能安全问题;以及在器件级别,选择leakage水平较低的工艺,如FD-SOI。”

高挺挺表示芯思原所做的低功耗架构“比较复杂”,最终令其BLE MCU芯片无论是RTC & GPIO wakup还是仅SRAM保持的深睡模式下都达成优于竞争对手的功耗水平。虽说这些方案涉及到了不同层级,很多也与指令集关联不大,但RISC-V实施灵活性在此依旧可以认为是深度践行能效优化与低功耗方案的基础。

“共享生态资源”

第三点就是RISC-V开放带来社区合作,共建生态的优势。活动现场最能体现这一点的无疑是RT-Thread嵌入式操作系统对于RISC-V的支持。上海睿赛德电子科技有限公司创始人熊谱翔表示,“无论是官方团队,还是RT-Thread开源社区,我们对于RISC-V架构的支持,都是丰富且完备的。”下面这张图给出了RT-Thread对于RISC-V,从IP核,到BSP和板卡,以及更多生态周边的支持情况。

本文不对这部分生态建设的内容做赘述,即便这些实则是最能体现RISC-V生态走向完善的。熊谱翔这次在演讲中主要谈的,是RT-Thread对于多核RISC-V芯片的支持推进。多核架构通常可以分为异构多核(AMP)和同构多核(SMP)。

对于异构多核而言,甚至可以是不同指令集的CPU核心(如Arm + RISC-V)。异构多核在软件上的挑战主要在于,RISC-V经常是其中的小核(比如作为HSM信息安全核存在),故而资源受限;“此时,核间需要轻量级但高效的通讯机制”。另外如何做到多核场景下的高效开发和调试也是个挑战,包括是否在多种模式下开发,以及调试是否涉及多个系统等...

对于RT-Thread于异构多核的支持,包括Linux负责复杂工作、RTOS用于实时控制,及Linux和RTOS之间用标准的OpenAMP通信:熊谱翔以K230举例,“大核运行RT-Thread Smart,小核运行Linux。大核会更多处理一些高性能负载,特别是AI相关的;小核解决功能性的任务。”“借助这样的支持,K230有了更快的启动速度。”

RT-Thread社区开发者则在RISC-V开发板milk-v duo上实现在大核(C906)运行RT-Thread Smart,在小核(C906,无MMU)运行RT-Thread。

“在AMP这种方式上,RT-Thread可以提供轻量级的、一套系统之间交互的框架、模式。比如说在系统之间通过RPMsg的方式进行交互,然后在此基础上提供远程的函数调用,做到跨系统的无缝、高效调用。”熊谱翔说,“资源占用问题上,因为小核对资源占用很敏感——我们提供的RPMsg方式,这一层提供很小的一套跨系统调用框架,code仅1kB,RAM只需256B,非常小巧和高效。”

而在异构多核之外的同构多核,“软件挑战更复杂”。就性能角度,包括负载均衡算法,且多核涉及到大锁、任务迁移、实时性等挑战;对cache和调试而言,同构多核都带来了不确定性。RT-Thread在v5.1以后的版本,对同构多核支持做了大量优化,包括“对大锁做出优化,将大锁拆分为小锁,提升多核性能”,包括在cache处理、调试器代码上的优化等。

熊谱翔还特别给出了基于上述优化,RT-Smart相较于Zephyr和RT-Linux,在同构多核之下的实时性能benchmark对比,如上图所示。此外还有面向多核RISC-V的集成开发环境支持情况,无论是All in One,集成了GNU GCC工具链、兆松工具链的IDE,还是VSCode RT-Smart扩展。

上面这些内容可能放在我们的RISC-V共享生态资源介绍中,显得有些过于具体了。不过这些的确就是RISC-V开发生态走向完善的表现,包括熊谱翔最后给出RT-Thread对于RISC-V的支持进展情况和未来规划,都能体现RISC-V相较两三年前的显著差异。

安全方向上的进化

有关RISC-V于嵌入式应用的优势第四点,“同等级的安全与可靠性”,恰好分论坛现场有两家企业是着重谈“安全”的——虽然这里的安全特指security:分别是芯来的Nuclei TEE,以及Rambus的信任根(Root-of-Trust)产品。

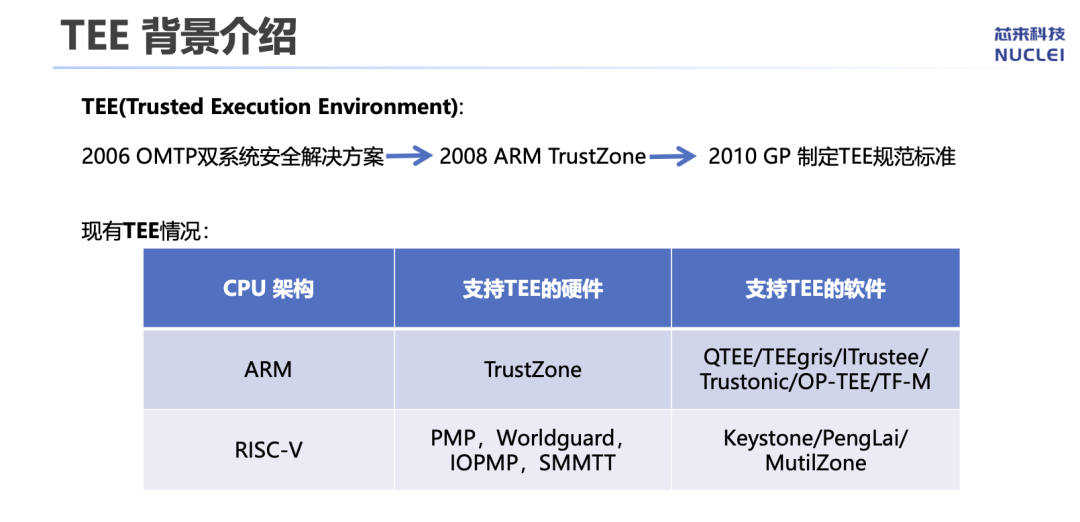

芯来的TEE(Trusted Execution Environment)方案着眼于对标Arm TrustZone——也就是所谓的安全世界或者叫可信执行环境,提供执行隔离。芯来科技高级工程师桂兵在主题演讲中说RISC-V生态内并没有足以对标TrustZone的完整方案,或者说现有方案是不够成熟的。

所以参考Arm面向Cortex-A和Cortex-M的TrustZone实施方案,以及RISC-V现有的安全机制,芯来分别推出了Nuclei AP OP-TEE方案,以及Nuclei MCU TEE方案。AP级与MCU级方案在安全模式划分、内存隔离和中断控制支持上存在差异,满足不同应用需求。

TEE本身是个还比较复杂的议题,感兴趣的读者可以去找一找相关文档做更详细的了解。至少芯来愿意主动去谈TEE,并提出自己的解决方案——而且应当可以实施到现有芯片产品之中(UX900, N300),也是国内RISC-V生态发展进度的重要一笔。

而相对更能体现RISC-V灵活性达成安全属性加成的,应当是Rambus亚太区业务发展总监姜新雨提到的,“封闭指令集架构无法像RISC-V开放可扩展架构一样,选择自己的指令和模块,以及用哪些机制控制来实现安全和相关的隔离。”这也让RISC-V芯片更容易在设计之初就导入信任根。

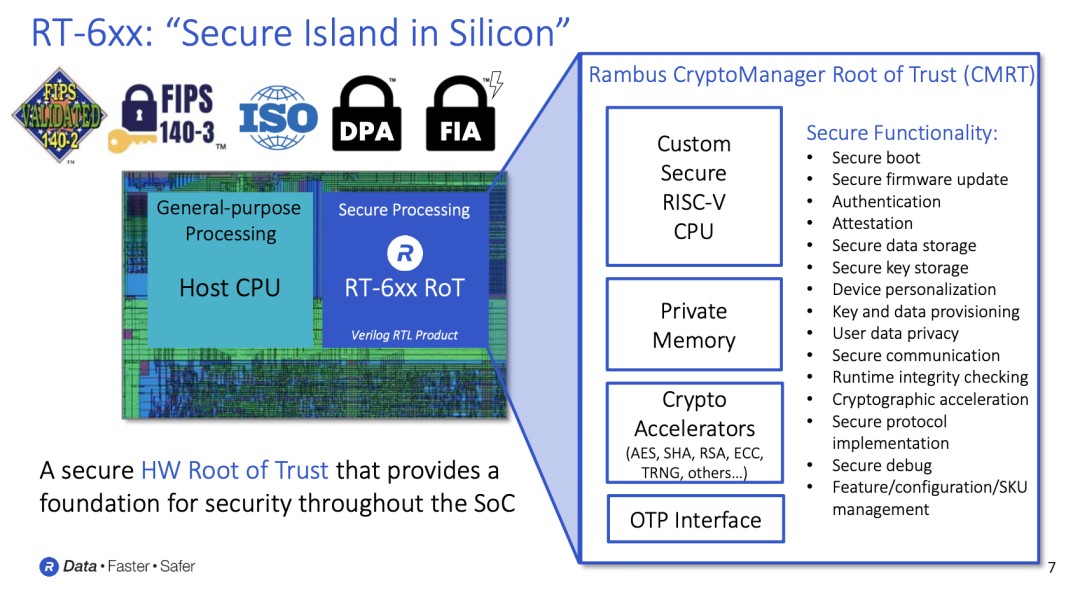

信任根(Root of Trust)提供SoC和应用能够用来构建起防护的信任基础;一般来说信任根产品面向SoC和应用提供强健的安全与加密服务,相关的安全功能可能包括安全启动、安全固件更新、身份认证、安全数据存储、密钥存储、数据加解密加速、runtime完整性检查等等。

Rambus的信任根产品(CrytoManager Root of Trust)具体为RT-6xx系列,下面这张图给出了其内部结构。“重点是这是个基于RISC-V的CPU,完全定制的内核,也有自己的安全内存;有丰富的加解密加速引擎,还有一些重要接口,与大芯片做集成,提供所有系统级安全功能,通过很多国际安全相关认证”,“可选配增加更强大的防物理攻击机制,像是防侧信道攻击的DPA保护,或者对抗错误注入的FIA保护。”

如果要谈此处的RISC-V CPU的话,Rambus更强调“从白纸开始”做设计,“专为安全应用打造定制CPU”(多级32bit RISC-V RV32I),所以才能达到在CPU管线执行阶段的DPA防护、shadow call stack逻辑、glitch保护等;与此同时,“由安全研究人员开发出来的安全微控制器,也便于安全实验室做审计”。

具体的软硬件架构,这里就不谈了。实际上Rambus的这个例子,倒是也更适合放在本文的第一部分“多样化应用场景”中,毕竟RISC-V在此更多扮演的是构成该安全结构的组成部分,且体现出了指令集的开放与灵活性。

更多本场嵌入式系统分论坛的演讲,受限于篇幅本文不再做单独呈现——包括奕斯伟详谈自家的RISC-V实时核IP布局和产品特色;以及Imagination谈他们在RISC-V生态上的高参与度(及其GPU IP内部就有个做调度的RISC-V firmware),及Imagination GPU + RISC-V CPU已经达成不少合作及对应产品的硅验证,如平头哥TH1520, 奕斯伟EIC7700X……大概都能充分体现RISC-V生态的建设进度。

最后值得一提的是许松在开场时谈到对于RISC-V长期发展“未雨绸缪”的建议,其中一点就在于面对传统架构的竞争压力,尤其“知识产权保护的挑战”时,要“建立专利联盟、开展联合开发:对内帮助企业优化各方资源、加速专利技术的落地;同时降低潜在专利风险”。

现阶段RISC-V市场之中尚未见到专利纠纷相关的法律诉讼,“可能因为生态还没有发展到一定体量与规模”,但先期的未雨绸缪仍旧是必要的,如此才能真正形成对于其他架构的有效长远竞争。实际上,2023年的滴水湖论坛上,RISC-V专利联盟就启动了。

我们当时就说那是RISC-V向前迈进的写照。从每年的RISC-V产业活动——无论是滴水湖论坛还是RISC-V峰会,都能看出RISC-V在发展生态过程中,对于所有先贤经验的吸收及取长补短,以及参与者们的积极和热情。这在科技行业的整个发展史中,都是不多见的。

责编:Ricardo

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊