5个问题,看清RISC-V在汽车领域的发展现状

- 2025-07-23 17:17:02

去年末的《汽车动力与底盘MCU市场现状研究报告》中,电子工程专辑稍稍谈到了RISC-V在汽车动力与底盘MCU这类高安全要求的领域仍然非常小众,技术层面也有进步空间;但我们也同时认为其发展潜力巨大,有机会在未来1-2年内更进一步崭露头角。

就RISC-V在汽车芯片领域的发展,有个关键事件也是研究报告中提到的,2024年8月英飞凌宣布会打造下一代基于RISC-V的MCU虚拟原型(virtual prototype),让客户提前在此基础上进行软件开发和评估。同时英飞凌还提到与博世、Nordic、恩智浦、高通合作组建初创企业Quintauris,加速汽车市场标准化,更进一步加速RISC-V的采用。

今年3月,英飞凌正式宣布汽车RISC-V MCU产品家族问世,归属AURIX系列——覆盖从入门级到高性能MCU。至此我们基本可以认为,RISC-V在汽车领域将迎来高速发展。最近RISC-V中国峰会的汽车电子分论坛上,芯来科技汽车业务发展经理范添彬在主题演讲中给出了下面这张PPT,显示RISC-V车规级CPU IP“已突破的关键领域”,和目前仍“待突破领域”。

“现有客户从电池前端很小的控制器,到网关控制、车身控制、整车控制、底盘控制等等。”“到今天,除了自动驾驶SoC主控,和座舱主控尚未采用RISC-V,绝大多数车载芯片都已经被cover。加上有相当优秀的合作伙伴去适配AUTOSAR,还有编译器、工具链、操作系统,这都是RISC-V在汽车领域突破的里程碑。”

可见RISC-V在汽车领域的发展,比我们想象得还要快。借着RISC-V中国峰会的汽车电子分论坛,我们尝试管中一窥地看看,RISC-V在汽车领域应用的现状及未来。

为什么汽车芯片要用RISC-V?

包云岗(中国科学院计算技术研究所副所长,中国开放指令生态(RISC-V)联盟秘书长,北京开源芯片研究院首席科学家)在峰会主论坛上表达过一个很务实的思考:对于企业客户而言,“Arm用得好好的,为什么要换RISC-V”?

中国国内的不少机构、媒体对于RISC-V的叙事,把大量注意力放在了技术自主可控的问题上——这可能的确是电子与半导体产业走向区域化之时,每家企业都不得不思考的问题。但从更务实、能产生盈利的角度来看,RISC-V势必需要具备技术优势,能为企业创造价值,才会让更多芯片企业、开发者主动迁往RISC-V。

对汽车市场而言,RISC-V更具体的价值究竟在哪儿?上海知从科技有限公司副总经理张志强谈到了RISC-V在汽车领域的四大优势,分别有(1)开放自由,RISC-V的开放模式让企业能够自由使用和修改架构,还能降低整车成本——MachineWare中国区代表吴铁阳就提到更灵活的方案,在技术和商业层面都有助于降本;(2)高灵活性与可扩展性,即开发者可以根据汽车应用具体需求来定制指令集;

有关这一点吴铁阳也在活动上特别谈到,RISC-V在助力EE电子电气架构的问题上,“当我们向智能汽车方向上走的时候,更复杂的场景可能会嵌入加速器、AI处理器之类的组成,RISC-V就能很好地满足这些场景——基于RISC-V设计这样的芯片结构会更容易”;

(3)高安全性:技术层面由于开放开源特性,更容易被发现和解决安全问题,另外也在于技术自主性;(4)高性能与低能耗——有关高性能,我们已经在主论坛报道中给出了更明确的解释,而低功耗很大程度也基于其灵活性特点,更优化的架构设计自然有助于降低能耗。

(5)另外还有一点,是兆松科技CMO胡灿在演讲中提到的: “RISC-V可扩展特性能够更好地满足SDV软件定义汽车的诉求。”从各方面来看,RISC-V都是个十分现代化的指令集。而上述几乎所有优势,都与其开放与灵活性特点强相关。

所以很自然的南京紫荆半导体首席战略官许兴奎认为,RISC-V有望与x86和Arm三分天下,“汽车电子将是下一个落脚点”,就像主论坛上几乎所有参会者所认定的那样——是几乎大部分应用市场的“三分天下”,从嵌入式到HPC AI。许兴奎列出的数据显示,今年RISC-V芯片出货量增长率会达到114.9%,芯片出货量级“12年就走完了传统架构30年的发展历程”。

量产芯片何时上车?潜力怎样?

RISC-V在汽车芯片领域虽然呼声很高,本次汽车电子分论坛的参会企业也涵盖了芯片设计、IP、软件等全方位市场角色,以及如文首所述,作为IP供应商的芯来已经列出了当前RISC-V指令集在诸多汽车子系统之中的应用,但至少现阶段RISC-V指令集在汽车市场份额仍只能归在others之列。

《汽车动力与底盘MCU市场现状研究报告》之中明确列出具代表性芯片产品就是来自长城汽车的紫荆M100——这颗芯片是在去年9月首次点亮的,当时媒体报道其为“国内第一个基于开源RISC-V架构研发的车规级芯片”。紫荆半导体是长城汽车内部孵化的汽车芯片设计公司。许兴奎介绍说,M100是“我们努力要做到的首个基于RISC-V架构、真正上车的芯片”。

目前M100芯片已经进入到了封装阶段,预计“9月份上车测试”。“长城对我们的要求是,上车即量产。”计划中M100真正上车大约是在明年Q1。介绍中提到,M100芯片的主要优势包括采用4级流水线,性能提升了38%;增强ESD,满足越野场景下对于静电的增强要求,“行业内大部分MCU芯片HBM都在4kV或2kV,CDM则为750V或1kV,我们做到了加倍”;还有安全性方面的加成等等...

紫荆半导体预期M100的应用场景包括仪表、氛围灯、电动压缩机、胎压接收器等方向,“整车大约17颗”。

除了M100这颗主要用于车身控制的MCU芯片,紫荆半导体规划中还有M200和M300,分别规划用在T-BOX、动力底盘这类更复杂的场景中。“M200正处在研发阶段,同样基于RISC-V架构,计划2026年底实现交付;M300正在规划中,今年底会启动研发。”另外据说还有正处在产品定义阶段的S300。

除紫荆半导体外,汽车电子分论坛现场另外一家芯片设计企业是武汉二进制半导体有限公司——这家公司2017年就转到了RISC-V指令集,2024年宣布“推出业界首款RISC-V架构、全流程自主可控车规级MCU芯片——DF30”,所以也是颇具代表性的。

这里所谓的“全流程”,武汉二进制半导体CTO陈永洲介绍说主要体现在四个环节:设计、制造、认证、应用——尤其在设计环节,成为“国内首个集成ASIL-D级RISC-V内核”。有关DF30芯片,陈永洲在介绍中提到ISO 26262 ASIL-D功能安全等级,AEC-Q100 Grade 1可靠性,支持多核锁步、高存储配置规格、安全加密算法、低功耗特性等...

加上在应用开发环境、软件方面的努力,据说二进制已经就DF30这颗芯片“联合多家头部车企完成发动机、安全气囊等核心控制器开发”。

上面这张图是二进制在汽车各功能域之上的MCU芯片规划——借此我们也能大致窥见,RISC-V MCU芯片在汽车市场的全面应用就在眼下了。

IP是否已经准备就绪?

除了芯片供应商的产品,生态要真正繁荣起来,势必要看价值链上的其他环节是否也同步完善,比如IP供应商。芯来的NA系列(Nuclei Automotive Series)即是为此准备的。范添彬在介绍中提到NA300, NA900, NA1000。“NA300对标Arm Cortex-M33/M4”,“NA900对标R52, A55;NA9000对标A76, A78AE”。

其中NA900和NA300都获得ASIL-D产品认证,据说NA900是“全球首个得到产品认证的RISC-V CPU IP”,“NA300则如法炮制”;与此同时“我们有计划NA1000也获得产品认证”。目前在汽车领域内,NA系列的授权客户数量已经超过18家,同时“4家大规模量产”,“这4家也取得了功能安全硬件的产品认证”。

范添彬在解释车规IP在实施、认证过程中遭遇的挑战和问题时列举CPU IP设计的硬件安全机制,“两大类”:(1)“物理实现相对粗暴的ASIL-D”,藉由冗余设计方法外加比较器确保一致性,“很多高性能核心不用这样的方法,因为芯片面积会增大,比较器还要拉很多信号出来”。

(2)而ASIL-B“采用的逻辑是,首先提供软件自诊断能力”——芯来有自己的STL(software test library),来发现硬件问题,“实现起来非常复杂”;另外还要加上DFF Parity/EDC(对关键寄存器做parity)、SRAM ECC等...

针对已经获得IP产品认证成果,尤为值得一提的是,“为什么很少有IP供应商和芯来一样做到ASIL-D产品认证,在于我们做了一些相当comprehensive的内容,我们的开发flow非常严谨地完成了功能安全标准”。

可举例的,比如CPU架构的FEMA(失效模式与影响分析),“我们是唯一一家在IP、微架构级会去做FEMA的。这种思路更像是将整车厂的FEMA经验搬到微架构实现上来,也是我们能够获得ASIL-D认证的原因之一。”还有面向SoC的DFA(设计失效分析)系统性分析工作等等......大方向在ISO 26262合规的问题上,从系统性故障和随机硬件故障两个方向上大量投入。

除了芯来之外,活动现场在RISC-V CPU IP方面另一个比较有想法的企业是阿里巴巴达摩院——且为域控制器形态。“一般为了兼容以前的生态,我们会基于AUTOSAR Classic平台(CP),把多种功能集中在一个处理器上,共享资源和外设。”阿里巴巴达摩院玄铁团队CPU架构师李伟立谈到,“各种功能或原来的ECU功能分时使用资源和物理机;各个应用间藉由通信接口通信。”

“应用会有不同的资产保护需求;它们之间需要相互隔离。”这就是玄铁预期中的域控制器工作形态,主要特色被概括为高性能、可配置、轻量化、实时、系统负担小、易开发、兼容AUTOSAR生态,以及符合功能安全标准。

相关于RISC-V的,这款域控基于RV32GCBV——包含矢量扩展,“提升运算能力”;支持M/S/U三个权限等级——做资产保护和安全隔离;另外可配置中断支持,和紧耦合存储器;“我们还留了个紧耦合协处理器接口,使用RV里面预定义的寄存器,也就消除了做其他扩展或通过memory扩展时同步带来的延迟,也有了更好的运算能力。”

加上“兼容RERI”,支持多核调试,满足ASIL-B/D标准,以及支持半虚拟化。除了常见的实时特性、可配置选项之外,“半虚拟化方案的思考”也更有趣。所以需要做虚拟机管理、执行权限管理(尤其区别于全虚拟化)、内存访问控制、中断虚拟化管理,和调试权限控制,实现多操作系统和应用的安全隔离。

李伟立还提到这款域控的ASIL-D和ASIL-B实现方案——与芯来形容的大致相仿。包括他也说到在“ASIL-B模式”实现上,在采用软、硬件结合的方式达到故障诊断覆盖率要求的问题上,ASIL-B“实现难度比ASIL-D更大”,“ASIL-D的逻辑很简单,两个核做lockstep,做一些输入输出,以及中间关键节点检查,保证一致性即可”,而“ASIL-B为了节省资源,要在软件层面通过各种方式,主要是程序执行或查点的方式,达到要求,这方面我们会做大量工作”。

当然,汽车领域内的RISC-V IP供应商中的强者还有不少,比如这次在RISC-V中国峰会上风头正劲的奕斯伟计算。受限于篇幅,本文不再赘述。

安全问题解决得怎么样了?

这个问题太大,我们只能基于分论坛演讲片面作答。范添彬在演讲近尾声时,对RISC-V对比竞品有个很有趣的见解:“其他指令集核心的功能安全未必比RISC-V强,但更高的安全性就是RISC-V要翻越的门槛——唯有具备真正的安全能力,减少客户的certification流程、减少解释成本,同时保证高质量、确保丰富的可配置性、满足客户需求,才能真正得到发展。”

活动现场的几乎所有来宾都在谈安全,包括safety与security。上海洛轲智能科技有限公司智能驱动研究院院长孙俊甚至从头至尾都在谈对功能安全的认识。“功能安全旨在将因系统失效导致的风险降至社会可接受水平。”而功能安全的实现依赖于完善的管理体系和开发流程,要求企业构建功能安全文化,明确职责分工,并在产品生命周期早期进行item定义、危害分析(HARA)及安全概念设计。

而企业要做符合ISO 26262标准的功能安全开发,“并不是从0开始”,而是补充传统V模型开发流程,强调ASIL等级的继承贯穿需求、设计、验证等各阶段。通过严重程度、暴露度和可控度评估危害风险,确定ASIL等级,安全目标及技术需求均需继承该等级,确保开发全流程符合安全要求。除了前文已经提到的安全架构设计(如锁步内核、watchdog等),孙俊在谈软件开发实践时,特别提到功能安全要求软件模块明确ASIL等级,设计文档和验证流程均需符合相应安全等级,确保软件开发环节的安全性和可追溯性。

值得一提的是,它特别强调某些企业获得ISO 26262流程认证,这更多“是对组织流程和产品开发流程的确认(功能安全管理体系认证),并不验证产品的功能安全属性”,故而要警惕很多企所谓“功能安全已达成”的表述。这也是我们每次在谈ISO 26262时所说的,流程是基础,并非安全的终点。

另一个在论坛上特别谈“安全”话题的是晶心科技——不过晶心科技辜善群谈的是security方向,即信息安全范畴——这也是汽车走向智能化、网联化的过程中尤为值得关注的话题。辜善群在演讲中提到,2024年汽车安全漏洞之中,与芯片相关的漏洞占比超过一半,而网络攻击带来的损失达到225亿美元,相比2022年增长20倍——尤以数据泄露的问题最大。

他所述“安全框架”的技术方向比较细节,特别去剖析的是与隔离相关的RISC-V安全构成,包括虚拟化实现所需的存储隔离(memory isolation)、中断隔离(interrupt isolation);细致到谈存储隔离中的page-based/TLB-based(基于TLB),以及register-based(基于寄存器)方法。

由于TLB cache miss的存在,延迟不确定性对实时性要求较高的系统而言是不可接受的,所以register-based隔离方案相对的“最大优势在于存储权控制的延迟是可确定的”,所以晶心科技的安全框架AndeSentry就是以基于寄存器的隔离方法为主,“REE OS是例外,它可以有条件地使用MMU,因为它不会被赋予实时性要求高的任务”,“可以使用生态系统更丰富的OS,如Linux, Android,或者MMU-based Zephyr。”

对于中断延迟优化的问题:中断处理分为两部分。硬件部分中断信号经平台级中断控制器(如PLIC或AIA)路由至指定核心并触发ISR。软件部分包括中断源识别(claim)和中断完成通知(complete)。多操作系统共用一个Hart时,ISR需进入虚拟化层,增加上下文切换延迟,数百至数千个周期不等;而操作系统独占Hart可直接跳转ISR,显著降低延迟。因此,实时系统优先采用OS独占Hart的设计。

基于这两个基本议题,AndeSentry汽车安全合作框架“是基于车用处理器security相关的软硬合作框架”。上面这张图使用晶心科技的AX46MPV-SE——作为安全CPU,且有矢量扩展;虚拟化层方面,考虑用执行在M-mode的hypervisor,用ePMP来隔离自己及其上运行的OS。

REE OS部分负责non-security和实时性要求并不高的任务,TEE OS用sPMP来做隔离;控制DMA采用了IOPMP;中断则基于AIA方案,“它能提供更好的弹性和可扩展性,还节省了ePMP的资源”。

不过这应该只是security议题之中很小的一部分,而且以上只是我们的高度总结。感兴趣的读者可以前往进一步关注AndeSentry安全框架。AndeSentry的提出,一方面体现了晶心科技推动开放、安全、可验证车用芯片生态的努力;另一方面,在我们看来这类话题的细致讨论,本身可见RISC-V车用芯片生态正逐步走向健全。

操作系统、基础软件、编译器、软件工具链情况如何?

这场汽车电子分论坛活动的大部队,实际上还是以做软件的企业为主——包括面向RISC-V的操作系统、基础软件、开发编译器及工具链支持。起码从这些参与者数量上来看,RISC-V的汽车软件生态走向成熟,似乎也是板上钉钉的。

下面这张图是芯来给出的RISC-V汽车生态系统,几个层级的主要参与者。范添彬说经常有Tier 1询问该生态内,compiler、RTOS、AUTOSAR等是否适配成功,“其实已经有先行者走在了前面,这些都已经不是RISC-V上车的阻碍了。”

经纬恒润、知从科技都谈到了自家的AUTOSAR基础软件。经纬恒润2023年提出Vehicle OS软件平台,推行“软件定义汽车”理念,“基础软件定义,就是围绕底层芯片展开的一些强相关的软件”。对于AUTOSAR CP,据说恒润从2018年到现在自研了几十个基础软件模块,面向包括MCU, 通信加速器, MPU, HSM等。

知从则提到汽车软件生态中的协作挑战,包括“内核架构改变,软件开发移植要求就会很高——即使AUTOSAR有分层概念,工作量依旧可能很大”,软硬件解耦、标准化工具链缺失等,都是问题。

张志强认为,RISC-V指令集本身就能缓解这些问题,这是RISC-V的开放性、社区合作基础决定的,尤其在所有参与者都按照开放标准去做的情况下。

他本次主要介绍的是知从科技的AUTOSAR基础软件“木牛”,强调RISC-V定制化指令集与架构分层设计,功能安全库与信息安全库的联动设计,以及开发环境深度融合。“实时性扩展(如精确时钟管理)适配AUTOSAR OS调度”,“安全扩展(如内存隔离)满足ISO 26262 ASIL-D”,并且“定义统一外设驱动接口(如MCAL),实现跨平台移植”。

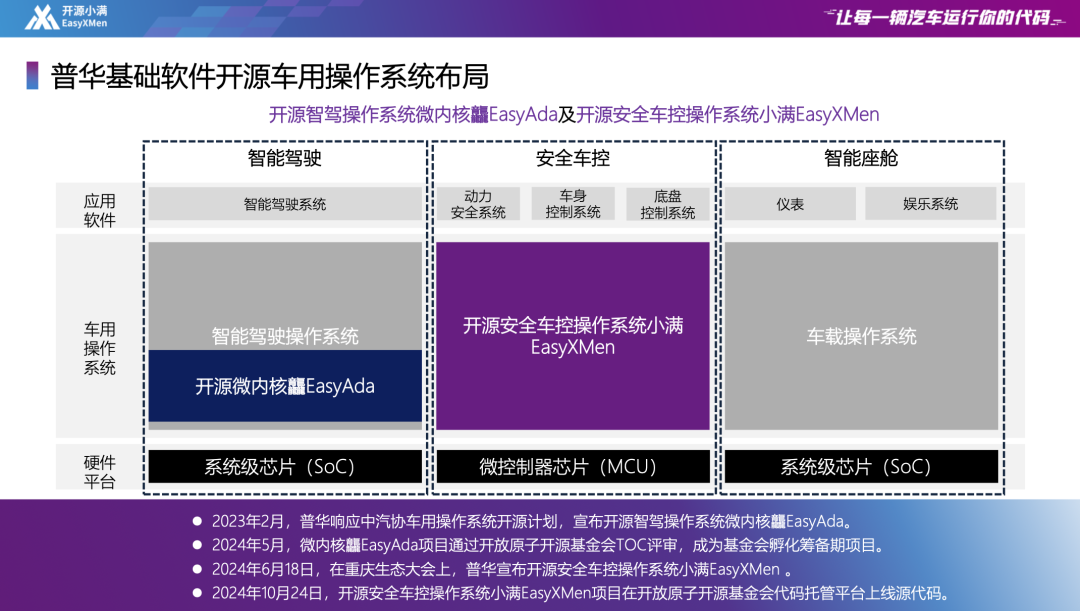

更相关操作系统的,普华基础软件股份有限公司副总经理兼战略研究院院长张晓先介绍了普华的两个开源项目:开源微内核龘EasyAda,以及开源安全车控操作系统小满EasyXMen——“这是依据AUTOSAR CP(Classic Platform)开发的计算件,但我们按照汽标委在标准中的定义叫安全车控操作系统,实际上就是汽车的基础软件”。

目前“龘”微内核有20000行左右的代码,“采用第三代微内核架构,代码自主率100%”,“支持异常与中断处理等标准核心功能”,“也支持POSIX线程调度策略,支持硬件抽象层”,“很容易适配不同架构的芯片”。另有基于龘EasyAda微内核的hypervisor,不过该hypervisor目前还不支持RISC-V。

龘EasyAda可适配安全车控操作系统,也可以作为安全操作系统、智能驾驶操作系统的底座,“我们希望做到既有安全特性,又能够有高性能和实时性的内核。”

而小满EasyXMen是在去年程序员节上线开源的,已经可以在AtomGit、Gitee和Github上申请使用(工具未开源,但可以免费使用)。据说已经有37家整车企业、342家零部件企业下载使用,不乏头部厂商;160所高校,累计下载和克隆数量超过2万次;“今年初,中国一汽已经向开源小满贡献了其轻量化安全组件”。

回到RISC-V,去年普华与玄铁团队合作,完成了RISC-V芯片架构的适配,并在社区发布了RISC-V代码分支。“上线新32位(RV64ILP32)代码”,“支持RVA(B) Profiles”。目前完成适配的包括矽力杰SA32B系列MCU、SA32D系列RISC-V MCU;开源小满RISC-V代码分支也已经在嘉楠科技K230D(玄铁C908)和HiFive Premier P550 KVM中成功运行,体现出对于psABI的支持。后续还有更多规划中的芯片预备上线。

IAR的软件工具链也是现场不少演讲嘉宾均有提及的。IAR Systems China高级工程师潘锋在演讲中介绍说IAR Embedded Workbench做到了“架构无关”:这是个一站式解决方案,可用于代码编写、编译、debug;单一IDE就支持多架构,包括RISC-V,所以“从其他架构开发项目可以快速迁移到RISC-V”;提供跨不同架构的多核开发与debug能力。都有助于解决前面提到的这些难题。

潘锋举例提到有客户做Arm + RISC-V多核芯片开发(上图),“我们很早就提供多核异构支持,甚至是完全不同的CPU架构调试方式。典型应用就有芯片厂商主核基于Arm,信息安全核HSM用RISC-V。我们的方案就能满足两种核的调试。”此外潘锋还介绍了IAR Build Tools for RISC-V...

IAR现阶段似乎反复在强调架构无关性,以及“RISC-V + x”的开发方式,“不需要采用不同的开发方式”,“不需要将时间放在部署工具链的流程中”——看起来,软件工具链企业对于RISC-V的适配普遍是相当积极的。

软件生态相关的部分,最后来谈谈编译器。胡灿说,“编译器就是将上层的应用程序,翻译成0101文件给底层使用。”虽然GCC和LLVM很早也支持了RISC-V,但商业化方案具备高性能、可定制,且安全可靠、提供技术支持等特性。

“编译器也会影响功能安全,如果编译器把C代码翻译错了,就会影响到安全。”而且是TI2(影响安全)/TD3(检测出软件错误或防止软件出错的难度最难),最终达成TCL3评级(上图)。胡灿还详细解释了对于功能安全,软件工具的鉴定认证和操作流程。

“我们经过一年时间拿到了南德颁发的产品认证证书,达到ASIL-D等级。”胡灿所说的是兆松科技ZCC-FuSa编译器——和硬件有所不同的是,ASIL-D对应的也就适用于所有ASIL等级。“系统级别验证必然用到编译器。用一个通过认证的编译器,也就节省了后续系统级别做验证的时间与人力。”

值得一提的是,在RISC-V指令支持方面,兆松的编译器基于LLVM,“做一些优化和功能验证”——据说性能比开源GCC高出35%,代码密度优化42%(基于Dhrystone)。“RISC-V的所有基础指令和扩展指令都支持,乃至某些厂商的自定义指令,“我们都做进了车规级编译器里面”。与此同时,还配有自定义指令扩展工具ZIGen,“提供图形化界面可扩展自定义指令,输入指令形成插件包,加入到编译器里面就能支持了。”

HighTec的编译器工具多平台支持更不用多说,不仅是RISC-V,还“覆盖业内所有主流车用MCU产品”。HighTec中国区技术负责人温吉辉说:“我们的理念是,整车厂有多个芯片平台的,尽量在工具链上保持统一;而且我们也保证所有编译器产品,都通过功能安全ASIL-D评估。”计划中HighTec今年Q4会发布RISC-V Rust compiler。

值得一提的是HighTec新推RISC-V虚拟原型,基于英飞凌AURIX“下一代RC1做示例,给客户提供一套评估方案,在TC4, TC3芯片的基础上,如果客户想评估英飞凌RC1,就可以用这套虚拟方案”,“借助新思VDK、我们的编译器,以及劳特巴赫虚拟平台,可以像真的RC1硬件芯片一样做评估。”

如此一来,英飞凌的用户未来用RISC-V芯片之时,“软件开发可以平滑过渡”。

“上层软件会认为自己就是运行在实际的芯片上,这就是虚拟原型起到的作用。”谈到虚拟原型,前文已经提到MachineWare也是本次汽车电子分论坛的参会企业之一,比如在完整软件栈开发过程中,虚拟控制器也能提前进行功能的验证与测试;

吴铁阳说,“RISC-V VP可以提前开发整车软件,包括MCAL对芯片公司、Tier 1,包括OS之上的提前验证,包括AI算法和应用,都能在VP环境下开发。”“其价值体现在规划、开发、调试、部署、维护的各个阶段。

本文最后也以MachineWare中国区代表吴铁阳的一个观点做结:“RISC-V和其他指令集并不是对立关系,就好像家用轿车、跑车、SUV不冲突一样。选择何种指令集取决于我们的设计目标。”

从RISC-V中国峰会汽车分论坛之上参会企业的态度来看,似乎其中的绝大部分都相当认可这一观点。毕竟那些占汽车MCU市场份额大头的巨头们,也都在同时并行几条指令集产品线。

责编:Ricardo

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊