联发科智联未来的AI时代全景图(三):高速接口与封装革命驱动AI基础设施跃升

- 2025-07-11 09:59:50

【编者按】

本文选自Semi Version,深度解析联发科在COMPUTEX 2025的核心战略转型,全景展现其从移动芯片龙头向全域AI领导者的跃迁之路。通过梳理联发科在边缘计算(如Dimensity 9300+的68 TOPS NPU)、车用电子(Dimensity Auto平台)、云端AI ASIC(携手NVIDIA推出NVLink Fusion) 等领域的突破,揭示其“端到云”AI生态布局的野心。文章聚焦技术里程碑(224G SerDes、2.5D/3.5D封装)与商业合作(苹果、全球车企订单),为读者呈现一家半导体巨头如何以开放架构、定制化芯片与超算级方案,重塑AI基础设施的未来图景。欢迎感兴趣的读者转发与关注!

高速SerDes部署:从112G到224G

在云端AI芯片设计领域,高速串行接口——SerDes(串行器/解串器)——对整体系统性能至关重要。联发科很早就认识到这一点,并投入了大量研发资源开发下一代SerDes IP

2022年,该公司推出了其112Gb/s SerDes IP,专为小芯片(chiplets)和服务器组件之间的长距离、高速数据传输而设计。值得注意的是,仅仅一年内,联发科就推进到了下一个前沿,开发出224Gb/s SerDes IP,从而跻身市场上最先进的接口技术提供商之列。

这款224G SerDes解决方案专为数据中心AI加速器中的小芯片间通信而设计,并于2024年成功通过了硅验证。凭借其超高带宽,该技术使得多芯片(multi-die)AI加速器能够以最小的延迟和功耗开销交换海量数据——提供支持大规模AI训练和推理工作负载所需的互连性能。

通过达成这一里程碑,联发科不仅展示了其在高速I/O领域的前沿能力,也巩固了其作为先进云规模AI基础设施可靠赋能者的地位。

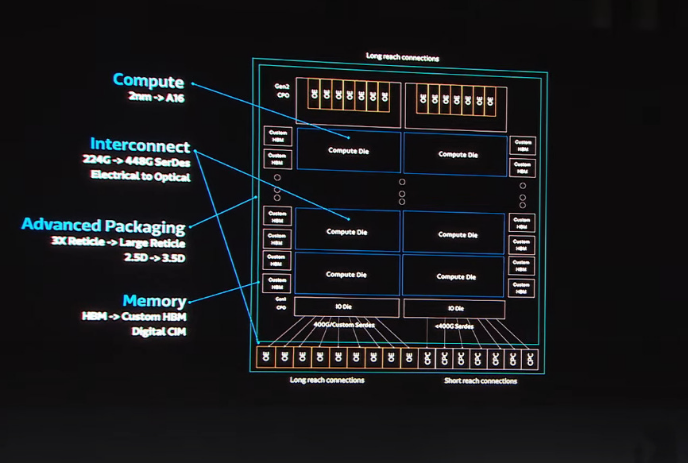

联发科计划继续突破SerDes技术的边界,目标是在不久的将来实现400G乃至448G的速度,同时也在积极开发共封装光学(Co-Packaged Optics, CPO)解决方案。随着芯片到芯片互连速度逼近每秒数百吉比特(Gbps),传统的电气接口正接近其物理极限,这促使向光学互连转变以降低延迟和功耗。

通过投资这些前瞻性技术,联发科正为自身定位,以在下一代AI基础设施中保持高度竞争力。首席执行官蔡力行强调,随着AI模型规模的爆炸性增长,未来的AI加速器将广泛采用3nm/2nm工艺节点、多芯片架构和高带宽内存(HBM)。这些加速器将依赖224G+的光电混合互连技术,来连接跨插槽、跨服务器甚至整个机架的芯片。

联发科在高速SerDes及相关互连IP领域的领先地位,使其能够满足超大规模数据中心对极致带宽和低延迟的需求。这种能力已成为一个关键差异化优势——也是联发科能在竞争激烈的全球市场中赢得AI加速器ASIC设计订单的关键原因之一。

先进封装技术的演进:从标准封装到2.5D、3D及3.5D集成

随着AI工作负载在复杂性和规模上的增长,传统封装方法已无法满足下一代处理器在性能、带宽和功耗方面的要求。联发科认识到,在AI时代,先进封装与尖端硅节点同等关键。该公司已逐步将其封装策略从标准倒装芯片设计演进至尖端的2.5D、3D以及新兴的3.5D集成架构。

2.5D封装:AI集成的基础

联发科最初涉足先进封装是通过2.5D集成,利用硅中介层(silicon interposers)将计算芯片(compute dies)与高带宽内存(HBM)连接起来。这种方法实现了高密度互连和更大的I/O带宽,构成了AI加速器和定制ASIC的结构骨干。值得注意的是,该公司成功使用2.5D封装开发出91×91 mm的多芯片AI芯片,证明了其在大面积、高复杂度模块方面的工程能力。

迈向3D与3.5D:垂直集成与混合架构

联发科认识到仅靠2.5D不足以满足未来需求,目前正向3D封装推进。在3D封装中,逻辑芯片和存储芯片通过硅通孔(Through-Silicon Vias, TSVs)垂直堆叠。这显著缩短了互连长度,降低了延迟,并提高了能效——这对于实时推理和生成式AI处理至关重要。

联发科也在探索3.5D架构,该架构将2.5D基础中介层与局部3D堆叠相结合,能够更灵活地将异构芯片(例如CPU、GPU、SerDes、HBM)集成到单个封装中。这些创新对于构建在尺寸、成本和性能之间取得平衡的超高性能、系统级封装(SiP)AI处理器至关重要。

先进封装中的战略合作与制造就绪

为支持这些封装创新,联发科与包括台积电在内的领先代工厂和OSAT(外包半导体封装和测试)合作伙伴紧密合作。它利用CoWoS(Chip on Wafer on Substrate)和InFO(Integrated Fan-Out)等技术,并积极参与开发兼容UCIe(Universal Chiplet Interconnect Express)和定制互连标准(如Mlink)的基于小芯片的架构。

此外,联发科的封装路线图还包括为光学I/O和CPO(共封装光学)集成做好准备,这与其高速SerDes开发(224G+)相协同。这些努力确保联发科能够满足下一代云和边缘AI基础设施日益增长的带宽和热密度要求。

战略重要性

先进封装已不再是一个后端工艺——它现在是系统级创新的前线赋能者。对联发科而言,掌握2.5D/3D/3.5D技术为赢得AI ASIC设计订单和扩展到云规模部署提供了竞争优势。该公司视封装不仅为一个实施步骤,更是与工艺节点和IP并列的、朝向全栈AI计算竞赛中的战略支柱。

随着芯片设计日益转向多芯片架构和异构集成,传统封装技术再也无法跟上高性能计算(HPC)和AI工作负载对性能的需求。联发科充分认识到先进封装的关键作用,将其视为与尖端工艺节点同等重要,共同赋能下一代硅芯片。

早期,联发科的移动SoC依赖传统的倒装芯片封装,这对于单芯片、单片设计来说是足够的。然而,在AI时代,处理器正变得更大、更具模块化且数据密集度更高。现代AI加速器通常需要将多个计算芯片、I/O控制器和数层高带宽内存(HBM)堆栈集成到单个封装中——这显著增加了设计和封装的复杂性。

为应对这些挑战,联发科正大力投资于2.5D、3D及新兴的3.5D封装架构,为自身定位以交付最苛刻的AI和云应用所需的性能、密度和可扩展性。

AI时代的转型:联发科市场地位与技术声誉的提升

随着联发科从消费电子芯片制造商转型为AI技术的关键参与者,其市场地位和品牌认知均得到了显著提升。传统上,联发科被视为提供中端智能手机芯片的供应商,在高性能计算领域存在有限;而近年来,该公司通过在AI领域的一系列决定性举措重塑了其形象。

拓展市场地位:从智能手机到云与汽车AI

通过进入汽车和云端AI ASIC市场,联发科开辟了智能手机之外的新战线。它现在占据了全球智能手机SoC市场超过30%的份额,与高通展开正面竞争,尤其是在5G时代。在移动领域之外,该公司还在智能电视、Wi-Fi 7路由器和物联网设备中扮演重要角色,形成了强大且多样化的产品基础。

这一基础,结合联发科日益增长的AI加速器业务,创造了一个从边缘设备到云基础设施的全面产品栈。正如首席执行官蔡力行所指出的,世界上很少有公司能提供连接边缘与云的AI解决方案,联发科正积极定位自身,以成为AI数据中心的核心技术提供商。事实上,联发科已经赢得了超大规模云客户的重要设计订单,预计收入将于2025年下半年开始产生。华尔街分析师认为,联发科进军定制AI芯片领域可能开启一个价值数十亿美元的潜在市场,成为该公司的下一个增长引擎。

*原文媒体:Semi Version

https://tspasemiconductor.substack.com/p/towards-the-core-of-ai-mediateks

相关阅读

芯启未来,智创生态

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊