“USB接口PCB设计全攻略|从Type-C到高速布线,一文掌握核心要点!”

- 2025-07-27 09:00:00

靠近板边:USB接口需伸出板边3~5mm,便于插拔(图2)。

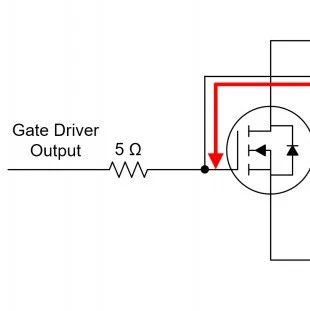

ESD与共模电感布局:ESD器件应紧邻USB接口,距离接口≤1.5mm,后接共模电感和阻容滤波电路(图2)。

图3 差分打孔换层处添加GND孔

图4USB的布局

优先内层走线:减少外部电磁辐射,确保下方有完整地平面。

禁忌:避免跨分割,否则导致阻抗突变和噪声耦合。

减少换层:过孔会增加寄生电容,建议换层次数≤2次。

添加回流地孔:每次换层时,在差分孔旁放置一对地孔,提供低阻抗回流路径,降低信号完整性风险。

差分对内等长:长度偏差≤5mil,USB 3.1建议≤2mil。

对间间距:保持≥4倍线宽,防止串扰。

独立电源层:为VBUS(5V/12V/20V)划分独立电源区域,避免与高速信号层重叠。

滤波电容布局:VBUS引脚就近放置10μF+0.1μF电容,滤除高频噪声。

CC引脚布线:需匹配阻抗(90Ω),长度与其他差分对一致,确保协议通信稳定。

VBUS路径:大电流路径(如20V@5A)需加宽至80mil以上,并采用网格铜降低温升。

原因:阻抗不连续或回流路径不完整。

解决:优化过孔旁地孔数量,检查参考平面完整性。

原因:差分线裸露在外层或包地不充分。

解决:内层走线+两侧包地,接口处增加屏蔽罩。

END

近期好文推荐:

30年前的老万用表,藏了半辈子才懂!有些工程师的老伙计,比新仪器更懂时光的温度

拆解博世DS9370 360°红外探测器!400块的“全能探测器”内部到底啥样?

合作/推广/投稿/宣传/招聘 请加微信:15889572951

声明:本文内容及配图由入驻作者撰写或合作网站授权转载。文章观点仅代表作者本人,不代表科技区角网立场。仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

点击这里

扫码添加微信

扫码添加微信

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊