一文详解MOS的寄生参数及其影响!

- 2025-07-30 16:20:51

MOSFET,作为现代电力电子技术的心脏,凭借其高速开关与极低损耗的特性,在电源、电机驱动等领域扮演着无可替代的角色。然而,在追求极致性能的高速应用中,理想模型与现实表现之间往往存在一道鸿沟,其根源便在于那些“看不见”的寄生参数。如同最基础的阻容元件,每一个MOSFET内部都隐藏着一个由寄生电容、电感和电阻构成的复杂网络。它们是影响开关速度、产生振铃噪声、导致额外损耗的“隐形杀手”。因此,深入剖析并掌握其寄生等效模型,不仅是理解其真实工作特性的关键,更是进行精准设计、优化系统性能的必经之路。

本篇文章是对“3000字一次性讲透MOSFET参数!!”的补充!

主要寄生参数及其对MOS管的影响

上图是一个简单的MOS管寄生参数模型,以NMOS为例,G、D、S分别为封装好的器件外部的栅极、漏极和源极,G1、S1分别为内部器件的栅极、源极,Ld为漏极的封装电感,Ls为源极的封装电感,Lg为栅极的封装电感,Rg为内部的栅极电阻总和。

源边感抗:源边感抗是MOS管寄生参数中最为关键的一种,它主要来源于晶圆DIE和封装之间的Bonding线的感抗,以及源边引脚到地的PCB走线的感抗。源边感抗的存在会导致MOS管的开启延迟和关断延迟增加,因为电流的变化会被感抗所阻碍,使得充电和放电的时间变长。

此外,源感抗和等效输入电容之间会发生谐振,这个谐振是由于驱动电压的快速变压形成的。谐振会导致G端(栅极)出现震荡尖峰,影响MOS管的稳定性。为了抑制这个震荡,通常会加入门电阻Rg和内部的栅极电阻Rm。然而,电阻的选择需要谨慎,过大或过小的电阻都可能影响G端电压的稳定性和MOS管的开启速度。

漏极感抗:漏极感抗主要由内部的封装电感以及连接的电感组成。在MOS管开启时,漏极感抗(Ld)起到了很好的限流作用,有效地限制了电流的变化率(di/dt),从而减少了开启时的功耗。然而,在关断时,由于Ld的作用,Vds电压会形成明显的下冲(负压),并显著增加关断时的功耗。

阈值电压变化:阈值电压(Vth)是MOS管进入导通状态所需的门极电压。寄生参数的变化可能导致阈值电压的漂移,从而影响MOS管的导通特性。例如,源边感抗和漏极感抗的变化都可能引起阈值电压的波动,导致MOS管在相同的门极电压下导通电流的变化。

栅源寄生电感测试

寄生电感的存在会对栅极振铃产生显著影响。其中,栅源极之间(焊引脚和键合线)的寄生电感L是导致栅极振铃的主要因素。根据U=L*di/dt,开关速度快,即di/dt大,则在源极引脚寄生电感上产生的感应电压更大。

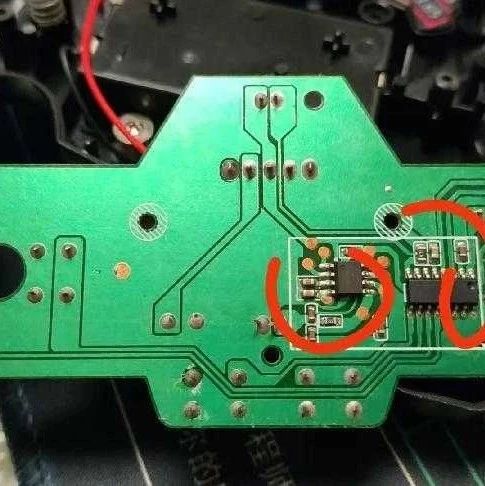

上面几张图,是大神实测栅源之间寄生电感振铃波形,大神直接把MOS管期间本身开了个窗,用探头直接测量封装内部的引脚G极和S极。这种方法可以排除键合点位置的寄生干扰,同时可以最直观地展示出差异性。

可以看到图a测试的是开启波形,外部测到的Vgs电压会在米勒平台处有13V左右的振幅,而内部的Vgs电压此时波动幅度非常小(轻微波动主要是电流和电压突变时电磁干扰影响)。

图b则是关断波形,外部测到的Vgs电压会在Ids突然下降时有很大负压尖峰(约20V)。而内部的Vgs此时几乎不变。

栅极振荡危害

导致EMI裕量不足 :下图是一款50W LED电源测试不同MOSFET波形和EMI辐射测试图。可以看到消除栅极振荡后,EMI低了6个dB。

动态负载切换振荡严重导致器件失效 :在某款电源动态测试时发现异常比例偏高,经过仔细测试分析发现该电源主开关管存在严重振荡现象。通过进一步对异常导致失效的样品进行Decap 观察,发现芯片表面栅极压焊点存在较明显烧伤。通过应用端分析,导致极振荡是电源在动态负载切换时,MOSFET存在较大的电流应力且电流变化较快。经过应用端PCB布局调整优化等措施后,减小动态负载切换MOSFET电流应力,VGS振荡明显改善。

END

技术干货推荐:

“USB接口PCB设计全攻略|从Type-C到高速布线,一文掌握核心要点!”

超实用!一眼能看出哪种拓扑:buck?boost?buck-boost?

PCB单层板LAYOUT,QFN封装的中间接地焊盘走线出不来怎么办?

合作/推广/投稿/宣传/招聘 请加微信:15889572951

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊