面板级封装,开始兴起

- 2025-07-25 17:57:06

这些组件的最佳开发方案是采用扇出型面板级封装,用面板取代目前的晶圆载体。扇出型封装的成本远低于硅中介层,同时能够容纳超大尺寸的芯片和高I/O数量。但设备方面仍需进行多项改进,以改善层间对准度,改进芯片/组件在基板上的倒装芯片贴装,并通过材料和工艺的进步来控制翘曲和芯片偏移。

面板级封装已被证明有助于降低智能手表、电源管理IC (PMIC) 和物联网设备等小型设备的生产成本。意法半导体 (STMicroelectronics) 用扇出型重分布层 (RDL) 取代了四方扁平无引线 (QFN) 封装中的引线框架。取而代之的是,它使用重分布层 (RDL) 进行连接,从而提高了生产效率并降低了生产成本。与通常与高性能计算相关的 2/2µm 前沿重分布层特性相比,此类设备所需的 RDL 线宽/间距要小得多,例如 10/10µm。

芯片制造商正在尽可能地围绕有机中介层进行整合,但玻璃芯也正在取得重大进展。

“我们或许正面临由高性能计算 (HPC) 和人工智能 (AI) 驱动的面板级封装第二波浪潮,”弗劳恩霍夫 IZM 组装与封装技术部门主管兼集团经理 Tanja Braun 表示。在第一波浪潮中,扇入扇出型 PLP 成为消费电子、汽车、高频和功率器件等成本敏感型应用的首选解决方案。第二波浪潮将应对使用面板级扇出型工艺处理尖端器件这一更为复杂的挑战。

Braun 表示:“目前,我们看到有机中介层技术和玻璃芯基板取得了很大进展,这最终是有机中介层的延伸,因为我们使用的玻璃芯两侧都有有机 ABF 层和 RDL 层。

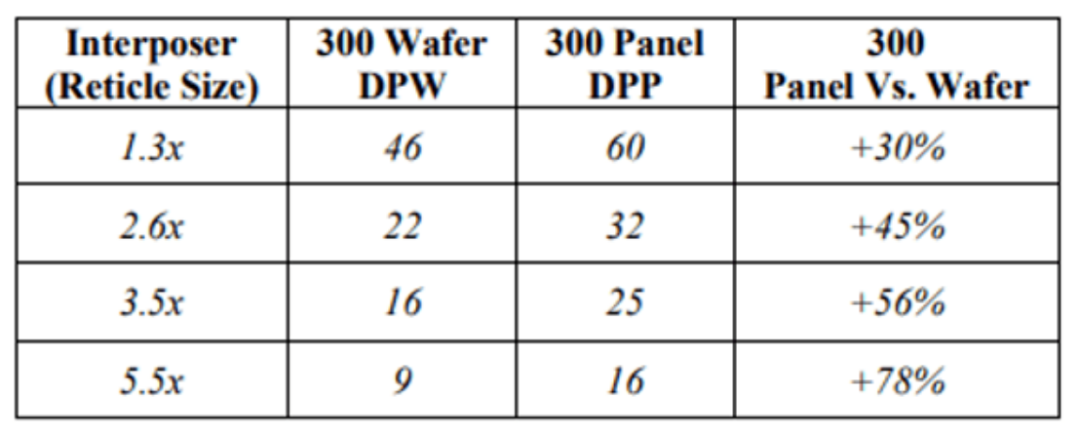

与晶圆级工艺相比,面板的载体利用率更高,从而提高了材料效率并减少了浪费。“为了实现更大的芯片尺寸和人工智能,我们需要在单个中介层中集成越来越多的内存和计算能力,”日月光研发技术总监Teck Lee表示。 “这是中介层尺寸越来越大的驱动力。”

图1:随着中介层尺寸的增大,面板级封装可以更好地利用载体面积,同时减少浪费。来源:ECTC

面板还将用于制造用于先进封装的基板。Yole集团半导体封装高级技术与市场分析师Yik Yee Tan表示:“我们了解到,台积电将使用面板载板支持9.5倍光罩尺寸的NVIDIA Rubin Ultra封装中介层。” 这意味着台积电将从CoWoS(晶圆基板芯片)转向CoPoS(面板基板芯片),在类似的300毫米尺寸上从圆形工艺转向方形工艺。我们认为,台积电在310 x 310毫米面板上积累了经验,并在未来考虑更大的面板尺寸。台积电还在努力开发515 x 510毫米面板。

从飞速增长的数据中,面板级封装的前景显而易见。Yole 估计,面板级封装市场规模将从 2024 年(1.6 亿美元,8 万块面板/约 33 万片等效 300 毫米晶圆)增长四倍至 6.5 亿美元,而到 2030 年,其规模将增长近三倍,达到约 22 万块面板。

面板尺寸取决于应用

面板尺寸取决于应用

图2:面板尺寸按年份分布。来源:Yole Group

Onto Innovation 产品营销战略副总裁 Al Gamble 表示:“面板尺寸的变化可以归因于制造商平衡所需容量、产量和 I/O 密度以实现封装功能的离散性。”

基板厂商青睐515 x 510 毫米尺寸。415 x 510 毫米尺寸用于医疗和工业显示器。SpaceX 计划在其 FOPLP 生产线上推出 700 x 700 毫米面板。Nepes 使用 600 x 600 毫米尺寸。与此同时,Amkor 正在为其生产线推出 650 x 650 毫米面板,每块 650 毫米玻璃面板可容纳 4 块 300 x 300 毫米面板。

日月光的Tek最近讨论了围绕310 x 310毫米面板的工艺变化,并制造了一个包含10个芯片、10个桥接器的裸片测试工具,其中包含高铜柱和3个重分布层(见图3)。“根据我们的分析,如果比较不同的中介层尺寸,300毫米晶圆和300毫米面板之间的利用率差别并不大。但当光罩尺寸大于3.5倍时,利用率会显著提高,面板浪费也会显著减少。此外,对于大于3.5倍光罩尺寸的封装,300毫米面板上的中介层质量要优于300毫米晶圆上的中介层。”

图3:ASE 的扇出型基板上芯片模块采用高铜柱(直径 10µm,高 120µm)、紧密的芯片间间距以及干净的底部填充工艺。来源:ECTC

光刻技术可补偿芯片偏移

光刻技术可补偿芯片偏移

“步进式光刻机在补偿因温度效应导致的芯片偏移方面效率最高,尤其是在存在明显刻蚀的情况下,”O'Toole 说道。“LDI 系统相对便宜。然而,一些采用复杂算法的更先进的系统可能与步进式光刻机一样昂贵,甚至更昂贵。而且 LDI 工具通常需要大量的离线测量才能完全补偿芯片偏移。”

其他人也认同LDI的局限性。Onto Innovation的Gamble表示:“基于激光的串行成像技术通常用于更大的RDL(再布线层)。但它无法提供所需的吞吐量来支持下一代技术的大规模生产,因为下一代技术需要更精细的RDL结构来支持AI和高级计算。需要通过低NA步进光刻技术进行并行成像——兼容最大250 x 250毫米的场域尺寸,并提供>30 PPH的吞吐量——才能满足产品上的成像要求(例如叠加、CDU和焦深)。这对于研发、良率提升和批量生产至关重要。反过来,这可以使总拥有成本达到基准水平,从而推动先进封装生产线的上市时间和盈利能力。”

虽然激光直接成像适用于较大的RDL,但为了达到更高分辨率RDL的图案化所需的吞吐量,需要使用多个激光器来降低生产率损失。当需要大批量生产时,这种损失会更加严重。使用多个激光器的激光直接成像平台容易受到拼接偏移的影响,无论是在扫描沿一个轴(例如y轴)传播时阵列内各个激光器之间的偏移,还是在扫描沿x轴移动时整个阵列的偏移。随着RDL L/S分辨率的不断降低,这些问题变得更加严重,通常会导致封装间和面板间重复性和套对合性能不佳。

先芯片、先RDL、先模具扇

先芯片、先RDL、先模具扇

图4:扇出型封装的不同工艺流程。来源:Fraunhofer IZM

先芯片(RDL 后)方法最为成熟,但它对良率的影响比后芯片更严重。Onto Innovations 的 Pau 表示:“先芯片工艺的优势在于其成熟度,这有可能降低制造成本。然而,它也面临着显著的挑战。一个主要缺点是加工过程中芯片移位和翘曲的风险,这会使重新分布层的缩放变得复杂。”

此外,RDL良率低会导致已知良好裸片 (KGD) 的损失,从而对整体效率和成本效益产生负面影响。“另一方面,在后芯片方法中,RDL 在连接 KGD 之前进行测试,从而能够及早发现缺陷并提高良率,”Pau 说道。“此外,这种方法支持更细间距的 RDL 微缩,因为它避免了通常由模塑料引起的额外翘曲。尽管有这些优势,但后芯片方法成本更高,并且要求将裸片极其精确地放置到载体上形成的 RDL 上,这增加了工艺的复杂性。”

其他人也同意这种观点。“如果你看一下先塑封、面朝下的方法,我非常喜欢它,因为它很容易集成不同的元件,即使是来自不同供应商、焊盘金属化程度不同的元件,”弗劳恩霍夫的 Braun 说道。“你有一个贴有离型膜的载体,然后把芯片面朝下放在离型膜上。你对大型晶圆或面板进行包覆成型,然后进行温度控制以释放载体。然后构建重分布层。在这个过程中,不涉及中介层,或者你可以说 RDL 就是中介层。先 RDL 就像一种先进的柔性倒装芯片工艺,因为你在载体上构建 RDL,然后在其上进行倒装芯片组装、包覆成型、底部填充,然后从载体上剥离。通常,你还需要硅减薄和蚀刻工艺步骤,最后进行 C4 凸块工艺。”

应对翘曲

应对翘曲

控制翘曲的其他方法涉及工艺控制。“C4凸块工艺的质量与载体剥离后的面板翘曲息息相关,”ASE的Lee表示。“一个关键因素是防止C4工艺过程中出现操作问题。”

载体翘曲问题已变得日益严重,以至于人们正在开发新材料来降低翘曲风险。台积电首席工程师Guillermo Zapico 表示:“翘曲管理已成为先进封装良率提升的关键要求。” 他的团队测试了日立杜邦微系统公司的一种非感光性聚酰亚胺,其热膨胀系数 (CTE) 与现有聚酰亚胺电介质相当,但固化温度却显著降低。他们发现,这种新材料能够满足蚀刻通孔的临界尺寸 (CD) 目标,同时在硅基板上将翘曲降低 79%,在陶瓷基板上则降低 95%。

结论

结论

如今,激光直接成像和步进式光刻机都在使用,但从生产率的角度来看,步进式光刻机更适合用于RDL图案化。同样,热压键合也经常被使用,因为它对翘曲问题的容忍度更高,而大规模回流焊则因其生产率而明显更受青睐。

随着新型层间介电材料以及膨胀系数更接近硅的成型材料的投入生产,制造商将能够更好地控制芯片偏移和翘曲。系统级优化将成为所有这些复杂的AI/HPC封装的重点。

AI PC产业研究报告

为帮助PC领域硬件层、软件层、模型层及终端层各类玩家更清晰地了解AI PC行业的发展现状及未来发展趋势,半导体产业纵横筹备撰写《AI PC产业研究报告》。现征集AI PC产业链各类厂商案例,该报告将通过半导体产业纵横全媒体矩阵发布,参与的案例可获得丰富的宣发支持和曝光机会。本次案例征集自即日起,报告预计7月发布,欢迎相关企业积极参与探讨!有意者联系我方商务:

* 微信号1: icviews2

* 微信号2: Joy8432211

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊