口碑载道,2025合见工软新产品发布会暨技术研讨会圆满收官!

- 2025-07-09 12:08:00

数百余位业内的工程师、研发、技术人员来到会议现场,合见工软凭借硬核技术实力,为客户带来了芯片硅前和硅后的高性能EDA工具和IP解决方案的现场全面展示,多项产品性能比肩国际标杆水平,得到了参会人员的充分认可及热烈反馈。合见工软坚持“以客户为中心”,聚焦用户需求,提供全面实时的响应。在自主可控和尖端前沿技术方面,全面助力我国自研EDA和IP产品从国产化替代到国际标杆技术的进阶之路。

会上,合见工软的技术专家以专业翔实的技术报告,向与会嘉宾展示并介绍了最新数字验证、DFT及高性能接口IP解决方案。

作为合见工软长期紧密合作的伙伴,多家国内领军芯片设计企业代表特邀进行分享:

燧原科技演讲嘉宾分享了《UVHS赋能燧原科技验证效能跃迁》的用户实践;

中兴微电子(Sanechips)演讲嘉宾分别就《Sanechips团队的UVS+/UVD+使用体验》及《UVHS助力Sanechips“珠峰”HPC芯片验证革新》的主题发表演讲,阐述了合见工软数字验证软硬件方案对其项目的关键助力;

北京开芯院演讲嘉宾带来了《香山昆明湖16核CPU完整系统的FPGA大级联系统验证实践》的经验分享。

以上客户分享均立足实际项目部署与真实用例,展示了合见工软创新技术如何有效推动芯片设计从蓝图加速落地。

来自行业近百家头部芯片设计企业、车企、高校单位以及科研机构参与了此次活动。其中包括来自燧原科技、中兴微电子、平头哥、达摩院、智芯微电子、比亚迪、云豹智能、复旦微电子、国芯微、紫光、辉羲智能、大唐电信、理想汽车、字节跳动、北京大学、清华大学、深圳大学等企业及学院研究机构的数百位验证工程师和科研技术人员,共同见证合见工软全新技术成果发布,并与合见工软的技术专家们展开深入探讨,碰撞出智慧的火花,在加深对前沿技术理解的同时,也为未来的技术创新与产业合作开拓新思路。

在上午的新品发布环节,合见工软五款年度创新产品重磅亮相,包括:

数字验证下一代硬件产品

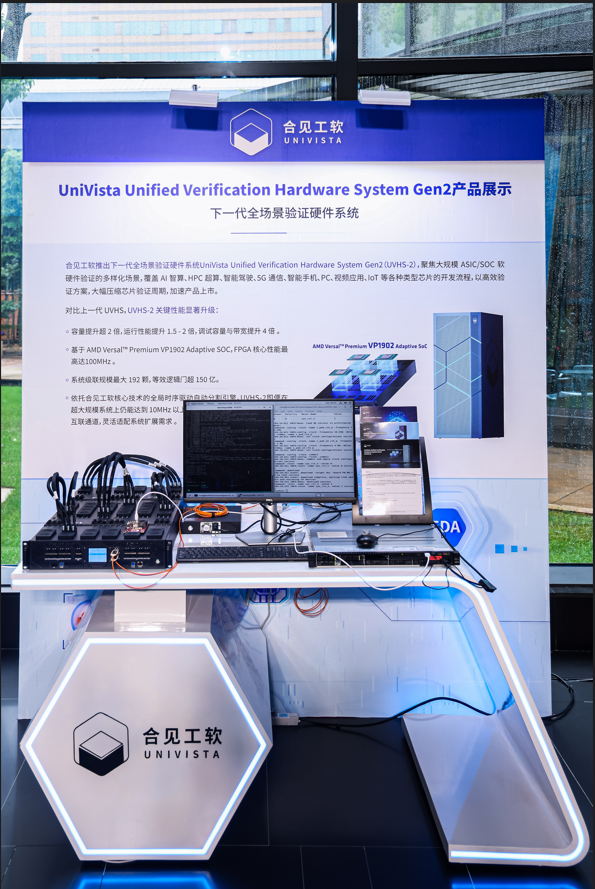

➤下一代全场景验证硬件系统UniVista Unified Verification Hardware System Gen2(UVHS-2)

国产数字仿真调试EDA重大进展

全国产自主知识产权高速接口IP解决方案

合见工软提出下一代EDA战略,将数字验证最核心的基础工具——数字仿真/调试器,及支持大规模芯片设计的高端硬件验证平台,均实现了架构级迭代创新,是国产EDA技术创新的重大进展,多项性能比肩国际标杆水平,目标打破数字高端大芯片验证EDA的国际厂商垄断。

同时,合见工软已在国内自研IP领域取得了快速的技术进展和客户增长,在国内自主自研高速接口IP的市场份额中已居前列。目前,合见工软的高速接口IP解决方案已实现了国产化技术突破,支持国内外先进工艺,并得到多家商业客户的成功流片和数百家客户的商业部署。合见工软的智算芯片互联IP解决方案,覆盖国内外先进标准,助力智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。尤其在当前国际先进EDA工具和制程受限的情况下,合见工软对高端芯片设计企业的产品与技术支持,助力了中国超算和AI类芯片企业打造自主可控的上下游供应链。

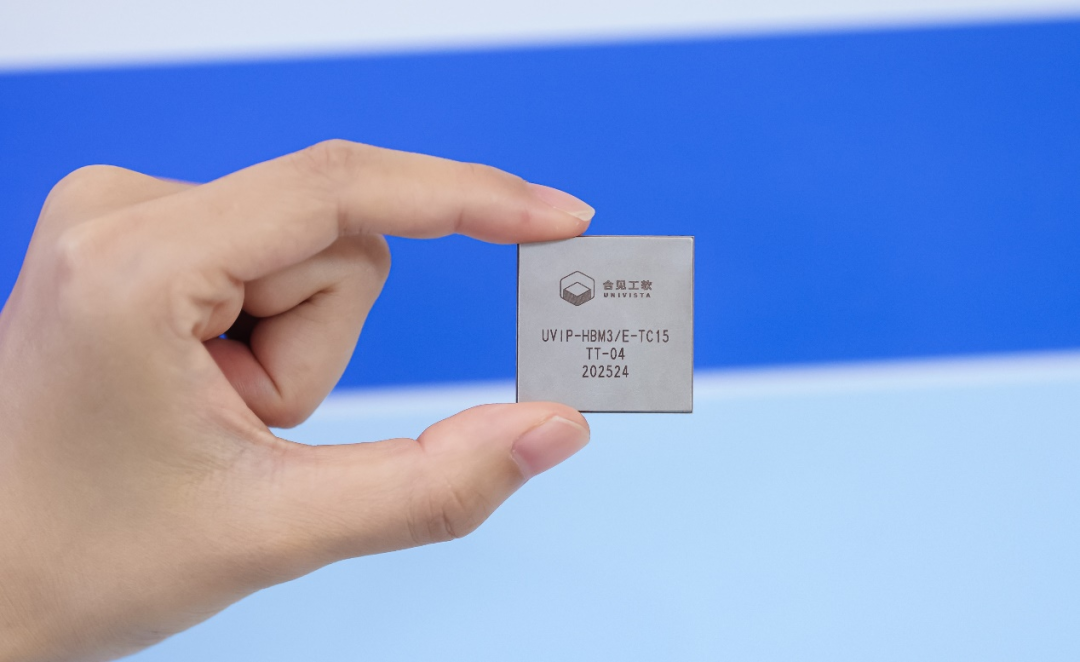

特别值得一提的是,在此次发布会上,合见工软宣布已经成功点亮HBM3/E测试芯片,基于标准电压实现高达9600MT/s的数据传输。合见工软提供高性能自研 HBM3/E IP控制器和PHY整体解决方案,控制器支持超低的读写延迟可以根据客户读写Pattern做定制化设计,加强的抗衰减和Deskew能力可以应对各种复杂场景设计,内置处理器可以灵活支持多种Training算法,完整的2.5D interposer和SIPI分析服务可以帮助客户通过端到端优化提升HBM3/E系统运行速度。自研HBM3/E控制器和PHY,广泛支持业界的各种颗粒,帮助客户在实际的系统中真正实现高性能。

▲先进工艺HBM3/E测试芯片

在下午的技术研讨环节,合见工软的技术专家团队带来了数字验证全流程EDA的详细产品介绍、视频操作演示、功能说明及技术实践。

UVHP大幅提升仿真验证效率

合见工软推出的数据中心级硬件仿真加速器UVHP是国产自研硬件仿真器中首台可扩展至460亿逻辑门设计的产品,该平台将硬件仿真系统的算力提升至数据中心级别,性能可与国际先进产品相媲美。

UVHP的特点在于高密度,能够支持更大容量的硬件仿真需求,特别适合部署在本地及异地远端机房、数据中心、公有云或私有云等场景中。此外,UVHP的编译与运行是解耦的,不受固定接口外设位置的限制,用户可以灵活地将编译好的工程在运行时再自动分配到可用的硬件资源上去,可大幅提升硬件的使用效率。

UVHP基于合见工软自主研发的新一代专有硬件仿真架构,采用先进的商用FPGA芯片、独创的高效能RTL综合工具UVSyn、智能化全自动编译器,以及丰富的高低速接口和存储模型方案,为超大规模ASIC/SOC的硬件仿真验证提供强大支持。

UVS+/UVD+比肩国际领先水平

合见工软最新推出的下一代全功能高性能数字仿真器 UVS+和下一代全功能高效能数字验证调试平台UVD+,标志着国产数字仿真调试EDA取得重大进展。具有全自研架构、全功能覆盖、高可靠性、易调试、高性能高容量等五大核心优势。

UVS+在大量真实项目严苛的实测考验中,稳定性与性能优势得以充分彰显,能够全方位、深层次地覆盖从模块级到系统级的芯片高效验证需求,为芯片设计企业提供坚实可靠的技术支撑。UVS+在单核编译和仿真性能真实项目、并行编译性能真实项目等测试得分中,比肩国际领先水平。

UVD+则实现了对调试全场景的无缝覆盖,拥有流畅美观的操作界面与便捷易用的交互设计,大幅提升用户体验。相较于传统产品,UVD+多维场景下在客户项目评分中的性能表现均可比肩国际领先水平。同时,UVD+还具有支持数模混合场景调试、低功耗调试、事务级协议分析以及覆盖率深度分析等关键优势功能。

此外,UVS+和UVD+还通过与业内领先的模拟仿真工具共建数模混仿联合方案、采用统一、开放的USDB波形格式、数据底座和组件开放等形式,拥抱国产上下游生态合作。

提高硬件验证平台Debug能力

硬件验证平台的Debug能力是保障芯片质量与研发效率的关键要素。芯片硬件验证平台包含FPGA原型验证平台和硬件仿真平台(Emulation)。相对于软件仿真平台,硬件平台有运行速度快的优势,但对Debug能力也带来很大挑战。

合见工软的专家针对FPGA原型和硬件仿真双模验证平台(UVHS)和高密度硬件仿真平台(UVHP),围绕如何进一步提高硬件验证平台的Debug能力,从核心的时钟建模与控制技术、动态可编程Trigger的技术原理、波形采样效率最大化的记录和重现应用、多种不同方式的全波形抓取技术性能与取舍等方面介绍了合见工软基于硬件仿真系统的深度思考和针对性的创新解决方案。

打造复杂芯片验证黄金组合

合见工软不仅具备IP设计能力,也将丰富的设计经验应用于开发硬件平台上的验证方案。为了帮助用户更快上手合见的产品,无论是IP还是硬件平台,合见技术团队将IP和接口验证方案整合在一起成了一系列的用户参考设计demo,从而大幅降低用户集成的时间成本。

比如通过提供PCIe5、以太网等多种高速接口速率适配器方案,将低速率的FPGA平台与高速的真实场景设备互联,确保验证的完整性,满足HPC、AI、汽车等当下主要的技术趋势的应用需求,并在行业中得到广泛部署。同时,合见工软也有世界一流的存储控制器Design IP和硬件平台存储模型Verification IP(MMK)开发团队,陆续开发了DDR5/4/3、LPDDR5/4/3、HBM3e/3/2e、GDDR6等先进方案,用户群体广泛,也是合见工软主要的技术优势之一。“高速接口x存储模型”方案已成为合见工软复杂芯片验证的黄金组合。

此外,面向AI芯片训练和推理等新兴场景,合见工软也能够提供包括Chiplet Die2Die以及Scaling Out/Up多卡组网等验证方案,具备优秀的商用级高带宽、低延迟、低功耗、协议完备等特性,可更好地解决芯片设计中的互联带宽受限、互联兼容等挑战,助力AI芯片的训练及推理。

支持多种验证模式支持

合见工软的全场景方案支持多种验证模式,包括纯硬件ICE环境、XTOR和Hybrid等方案,为芯片系统级软硬件协同设计及验证提供了强大的算力支持,同时确保用户验证工作的可预测性、效率提升和质量保障,同时满足多样化的用户需求。

针对UVHS/UVHP Emulation XTOR(软硬件协同仿真协议转换器)方案,合见工软的技术专家从XTOR的架构、技术原理、各种特定协议应用等方面,进行了详细介绍。并针对PCIe、MIPI CSI/DSI以及UART方案进行了讲解及Demo演示。

UV Hybrid方案是合见Emulation上的另一个新兴应用场景,具备灵活性强、仿真速度快、资源利用率高、易于调试等特点,可以让用户在开发效率、验证精确度、硬件资源使用成本等诸多需求上找到优化平衡点,进一步推动芯片产品加速面市。

茶歇期间,会场休息区成为了思想碰撞的新舞台,参会人员手持咖啡茶点,围绕在合见工软技术专家身旁。有人就会议中未能完全理解的技术难点寻求详细解答,有人结合自身企业在芯片验证中遇到的实际难题,请教针对性的解决方案,还有人探讨行业技术发展趋势,与专家展开深度交流,技术思维的火花在轻松的氛围中不断迸发。

技术展示区,合见工软带来了核心技术产品的产品展示,其中包括:

下一代全场景验证硬件系统(UVHS-2)实物产品演示。对比前代产品,UVHS-2实现了很多关键性能显著升级。包括容量提升超2倍,运行性能提升1.5-2倍,调试容量与带宽提升4倍;基于AMD Versal Premium VP1902 Adaptive SOC, FPGA 核心性能最高达100MHZ;系统级联规模最大192颗,等效逻辑门超150亿。

下一代高性能全功能数字仿真器(UVS+)和调试平台(UVD+)视频操作演示。UVS+全面支持Verilog、SystemVerilog、UVM等主流标准及验证方法学,并支持UPF、SystemC、数模混仿。X-prop等高阶功能,提供从RTL到门级、数模混合到低功耗验证的全流程解决方案。UVD+主要演示了智能源代码追踪、完整的FSM调试解决方案、灵活的双设计调试方案等功能。

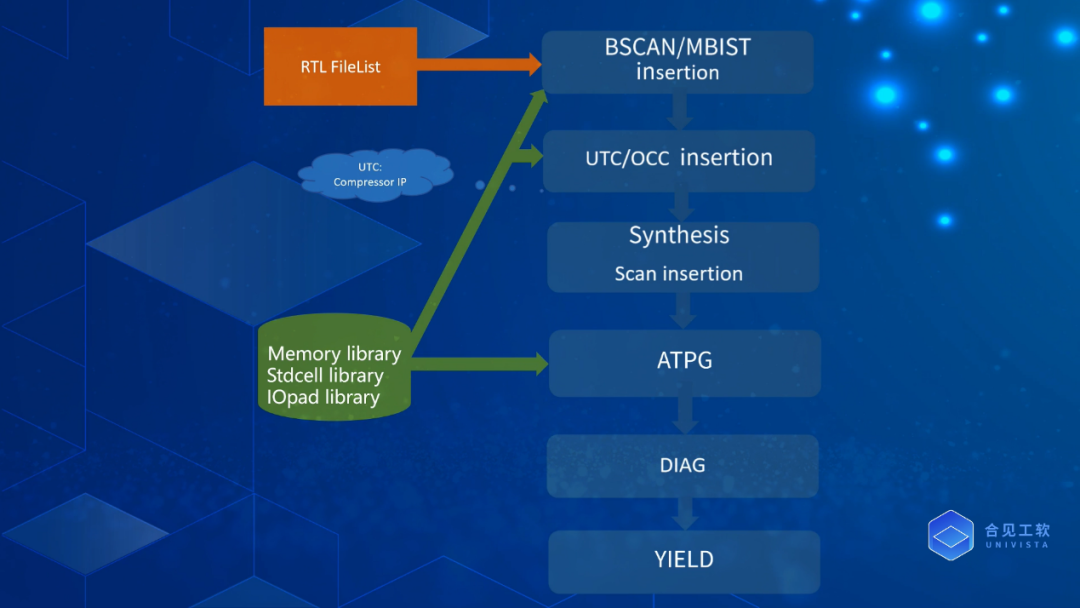

国产自主知识产权的可测性设计(DFT)全流程平台UniVista Tespert 的RTL DFT全流程视频操作演示。UniVista Tespert集成了一系列高效工具,包括边界扫描测试软件工具、存储单元内建自测试软件工具、测试向量自动生成工具、缺陷诊断软件工具、良率分析工具等一系列工具,助力芯片开发效率提升。

基于PD-AS的组网验证平台UniVista UEC MAC IP/ PAXI IP实物产品演示。UniVista UEC MAC IP可与合见工软原有的智算网络Scale-out应用解决方案UniVista RDMA IP和针对智算网络Scale-up应用的ETH-X传输层协议解决方案UniVista PAXI IP相互协同,进一步扩大了合见工软在智算芯片互联IP技术领域的优势。

此次合见工软三地新产品发布会暨技术研讨会的成功举办,离不开业内外朋友对合见工软的关注和支持,真诚感谢所有用户对我们的信任与一路陪伴!

多款创新产品的发布,彰显了合见工软在EDA领域的深厚技术积淀与创新实力。以硬核技术实力为底色,合见工软将持续为实现国产EDA替代注入动能。同时,行业人士的广泛的关注,客户的携手共进,是对合见工软最大的认可与信任,也展现出国内EDA产业蓬勃发展的势头与产业生态的繁荣。

展望未来,合见工软将始终以推动国产EDA技术进步为己任,持续加大研发投入,加速技术迭代升级,打造更多具有国际竞争力的产品与解决方案。期待与更多行业伙伴携手,构建更完善的国产 EDA产业生态,共同打破技术壁垒,实现半导体产业的自主可控,让中国 “芯” 在世界舞台上绽放更耀眼的光芒!

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情

请访问www.univista-isg.com。

点击“阅读原文”,立即访问合见工软微官网~

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

-

加入群聊

扫码加入群聊

扫码加入群聊