见证可测性设计DFT平台变革!合见工软UniVista Tespert“家族”上新

- 2025-07-11 12:09:00

合见工软现有产品已覆盖数字芯片EDA工具、系统级工具及高端IP,是国内唯一一家可以完整覆盖数字芯片验证全流程,DFT可测性设计全流程,并同时提供先进工艺高速互联IP的国产EDA公司。自成立以来,合见工软一直以国际先进水平为目标,多产品线并行研发,为中国半导体企业提供了芯片硅前和硅后的高性能EDA工具和IP解决方案。

今年以来,合见工软针对DFT平台进行了大幅增强。如果说去年解决了0~1的问题,今年则完成了1~2的跳跃,实现从满足中小规模芯片设计到迈向大规模芯片设计的进步。

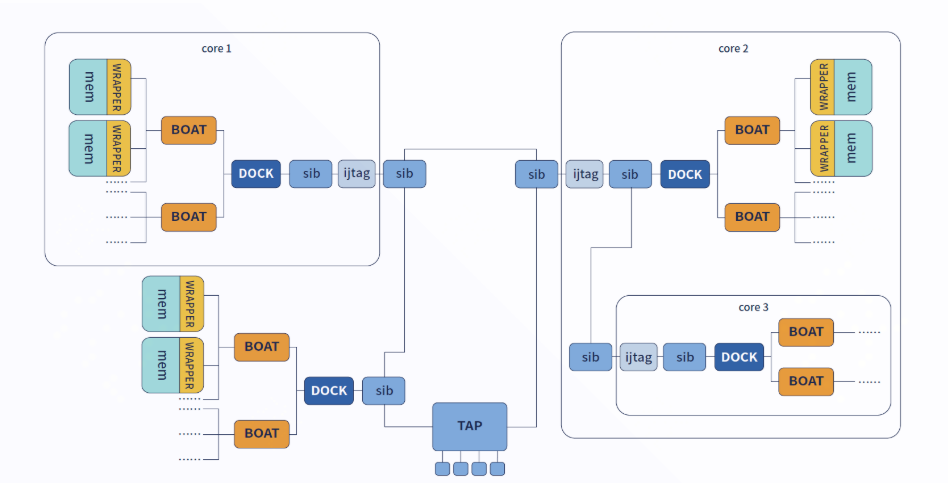

▲可测性设计(DFT)全流程平台

可测性设计(DFT)全流程平台UniVista Tespert是合见工软更广泛的数字实现EDA产品组合的重要产品之一。该平台集成一系列高效工具,其中包括:边界扫描测试软件工具UniVista Tespert BSCAN、存储单元内建自测试软件工具UniVista Tespert MBIST、测试向量自动生成工具UniVista Tespert ATPG、缺陷诊断软件工具UniVista Tespert DIAG、良率分析工具UniVista Tespert YIELD。

近年来,人工智能、数据中心、自动驾驶等行业迅猛发展,其对大算力的需求使得芯片尺寸和规模越来越大,单芯片晶体管多达百亿甚至千亿级别;同时,高阶工艺和先进封装如Chiplet等技术的应用,大大增加芯片集成度与复杂度,设计与制造过程中芯片出现故障的概率大幅提升,对芯片测试DFT解决方案提出更高要求。

芯片工程师需要快速精准地发现故障,修复或者避开故障从而提升良率;同时,需要进一步提升测试覆盖率,将一些测试流程左移,以减少缺陷逃逸率,避免增加成本或延误产品上市时间,合见工软推出的UniVista Tespert平台则很好地解决了上述痛点。

合见工软UniVista Tespert“家族”里首先出场的是——UniVista Tespert BSCAN。该产品旨在帮助用户在集成电路(IC)设计中实现边界扫描测试。该工具通过在每个PAD附近加入Boundary Scan Cell来实现对每个PAD的控制和观察,从而无需使用物理测试探针即可测试芯片IO功能和板上集成电路之间的互连,并能够对芯片进行无损检测,确保设计的可测试性,提高产品的测试效率,并降低测试成本。

▲UniVista Tespert MBIST 架构图

UniVista Tespert MBIST是一款先进存储单元自测试工具,集成了先进的IJTAG接口协议,可提供直观易用的图形界面,支持多种测试算法和灵活的设计规则检查引擎。该产品基于IJTAG的高效自动化流程;支持Flat和Hierarchy的设计流程;完备高效的memory测试算法;支持模糊匹配和精准匹配两种的SDC生成方案;支持DRC检查和自动修复;支持基于共享总线的MBIST流程;支持Memory Repair流程。刘培彦表示:“UniVista Tespert BSCAN/MBIST都支持逻辑插入和测试向量生成在一个流程里完成,也可以在各种独立的流程里完成。”

通常而言,集成电路的测试是整个集成电路设计和生产过程中不可或缺的核心环节,高品质、低成本的测试是保证芯片质量的关键,在此进程中,高效的测试向量自动生成工具UniVista Tespert ATPG是达成高质量测试的关键支撑。

▲UniVista Tespert ATPG 流程图

该产品可实现:基于IJTAG的高效自动化流程;支持Flat和Hierarchy的ATPG流程;支持并行多线程,提升ATPG pattern产生效率;强大的SDC File处理能力,保证高频测试质量;支持Low-power压缩IP和向量生成;支持CCD和UCP两种capture时钟控制方案;支持IDDQ和Path Delay 等pattern 类型。本次新品发布会暨研讨会现场,Flatten和Hierarchical ATPG两种方案均得以精彩演示,令现场观众感受到产品的强大功能。

UniVista Tespert DIAG是一款创新高效的缺陷诊断软件工具,其图形化界面提供了缺陷全景对照,帮助工程师快速定位和解决系统性缺陷,大幅提升芯片测试效率,加速产品上市时间。

目前,该产品支持——Hierarchical Diagnosis流程;支持Mixed-Failure Diagnosis流程;支持基于多线程的Volume Diagnosis流程;支持Layout-Aware Chain/Scan DIAG流程;支持Layout-Aware AC Failure DIAG流程;独创的FA-friendly Diagnosis Report;支持缺陷全景对照的GUI。据悉,UniVista Tespert DIAG拥有更高效的 Volume Diagnosis——每额外并行job只消耗10%~15% 额外的内存,可实现更大任务的并行运行。

随着半导体制造工艺的不断演进,良率提升已成为企业保持竞争力的关键。本次新品发布会暨研讨会上,刘培彦向与会观众介绍了公司今年3月推出的全新产品UniVista Tespert YIELD。这是一款以图形用户界面(GUI)为核心的良率分析和提升工具,其通过创新的图形化操作界面和高度自动化的分析流程,为工程师提供从缺陷诊断到根因分析的全流程解决方案,真正实现“开箱即用”。

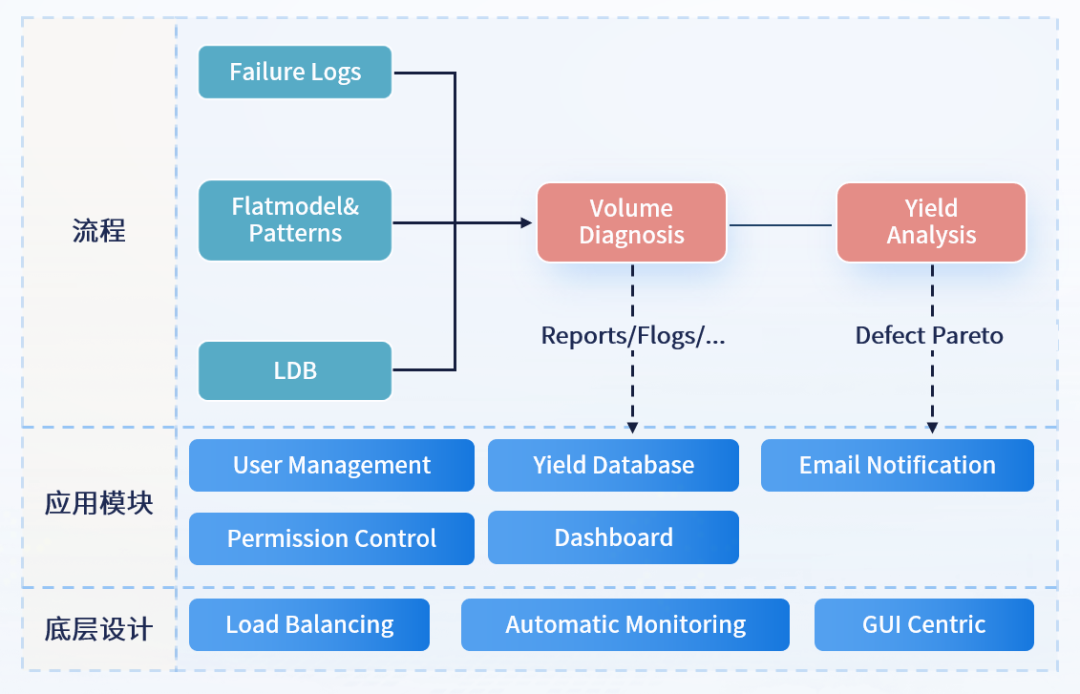

▲UniVista Tespert YIELD 流程图

该产品可实现:支持基于Yield Flow的全自动流程,提供一站式良率解决方案;支持Chain Failure RCA/FAA;支持AC Failure RCA/FAA;独创的FA Assistant系统,自动推荐最合适FA的die;独创的FA-Friendly诊断报告, 提升FA的效率;支持对于缺陷的灵活过滤和Wafermap/Heatmap展示;支持聚焦CELL的分析以及灵活的CELL分组策略……基于上述功能,UniVista Tespert YIELD在加速良率提升周期、降低成本、提升产品竞争力等方面优势显著。

作为致力于为工程师提供更高效、更高质量的完整芯片测试平台化工具,UniVista Tespert平台从推出起,即为满足现代芯片设计复杂度和封装技术挑战,助力客户提升产品质量和市场竞争力,该系列已在多个国内头部IC企业中成功部署,应用于超50多个不同类型芯片测试,在数字芯片EDA工具的高端市场上,全面展现公司产品竞争优势。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情

请访问www.univista-isg.com。

点击“阅读原文”,立即访问合见工软微官网~

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊