LDO与DC-DC串联到底能抑制多少纹波?

- 2025-07-03 12:44:36

实际上由于现在追求小体积,DC-DC的频率越来越高,也就意味着其纹波频率越来越高。为何频率越高体积越小?点击此前的文章了解:如何减小DC-DC芯片外围电路体积?

如下是TI的一款DC-DC,典型的工作频率为1.5MHz,那么参考上图,其1.5MHz下的PSRR大约为45dB,也就是能把纹波抑制为1/178。

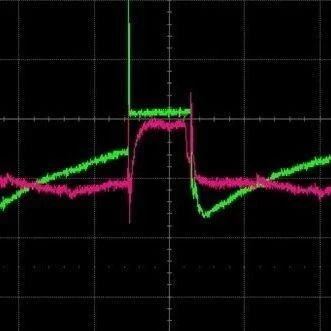

要注意的是,DC-DC在低负载下会切换为PFM模式,即其频率会降低,例如下图降低到了大约200kHz,在此频率下不仅DC-DC的纹波会增大,LDO的PSRR也会改变,因此在设计中也要关注不同频率下的PSRR,并且调试时测试不同负载下的纹波。

声明:本文内容及配图由入驻作者撰写或合作网站授权转载。文章观点仅代表作者本人,不代表科技区角网立场。仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

点击这里

扫码添加微信

扫码添加微信

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊