AI助力,RISC-V打破CPU世界“不可能三角”?

- 2025-07-21 13:23:40

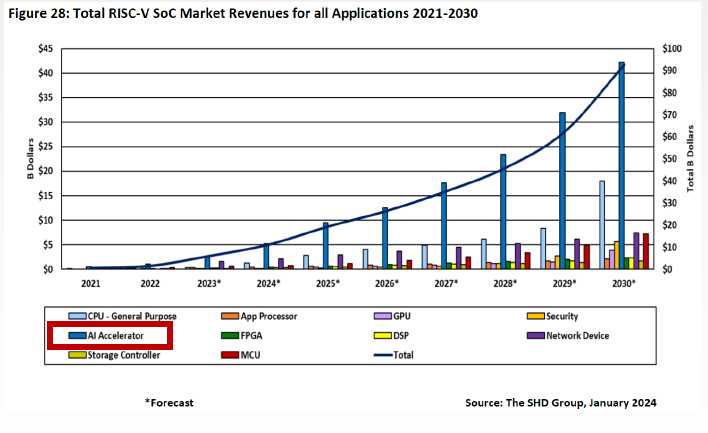

近年来受生成式

AI驱动,RISC-V芯片市场快速发展。根据The SHD Group预测,到2030年,RISC-V SoC出货量将达到1618.1亿颗,营收将达到927亿美元;其中,AI加速器领域将成为增速最快的细分市场,预计出货量41亿颗,营收422亿美元。这一趋势的背后,是大模型对算力需求的爆发,以及异构计算范式与RISC-V模块化、可扩展性技术的高度契合。

“CPU世界一直有一道不可能三角:自主可控、技术繁荣、商业成功,三者难以兼得。但是,RISC-V第一次让这三者同时出现可能。”7月17日,在上海举办的2025年RISC-V中国峰会期间,举办了一场主题为《RISC-V产业落地的机遇和挑战》的圆桌讨论,主持人、峰会主席戴伟民在开场白中说到。这场讨论汇聚了国内外RISC-V领域的头部专家、企业代表及学术机构负责人,聚焦AI算力革新、超低功耗场景落地、汽车芯片生态构建及工具链成熟度四大核心议题,揭示了RISC-V在生成式AI浪潮中的战略价值与生态潜力。

主持人:峰会主席,上海开放处理器产业创新中心 理事长 戴伟民

嘉宾(按姓氏拼音排名):

中国科学院计算技术研究所 副所长,中国开放指令生态(RISC-V)联盟秘书长,北京开源芯片研究院首席科学家 包云岗;

算能高级副总裁 高鹏;

合见工软CTO 贺培鑫;

奕斯伟计算高级副总裁、首席技术官 何宇;

芯来科技创始人 胡振波;

Tenstorrent首席架构师 Wei-Han Lien;

知合计算 CEO孟建熠;

中兴微副总经理 石义军;

芯原股份执行副总裁、定制芯片平台事业部总经理 汪志伟;

阿里巴巴达摩院 RISC-副总裁 杨静;

南京沁恒微电子技术总监、董事 杨勇;

新思科技技术执行总监 张春林

戴伟民指出,到2030年全球半导体市场规模将超过万亿美元,但是其中70%都与AI相关。他用“树干-树枝-树叶”比喻AI算力迁徙——训练是树干,端侧微调是树枝,推理卡则是即将爆发的树叶。去年火爆的 “百模大战”,AI大厂几乎把买来的所有英伟达GPU都放在“云”上,“而今后我们认为今后更多的算力将向端侧延伸。”

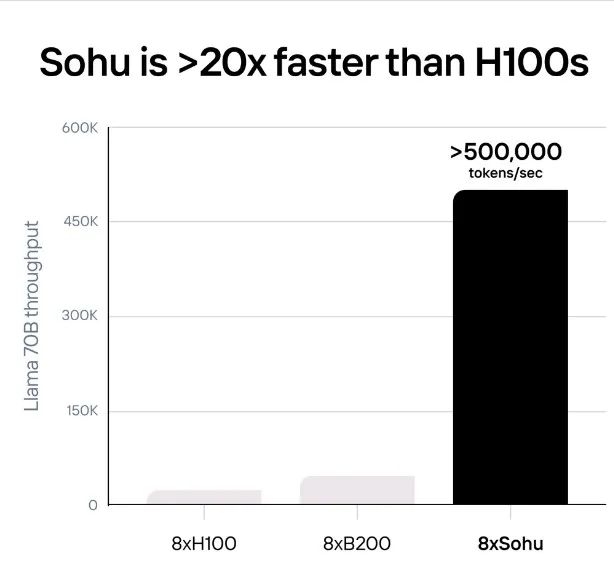

现在AI芯片主要分为两种——GPGPU和ASIC,而几乎所有大模型都还是基于Transformer。鉴于英伟达在GPGPU领域的垄断地位,初创AI芯片公司普遍选择从ASIC入手,针对Transformer做优化,由哈佛大学00后华裔学生Chris Zhu和Gavin Uberti于2022年创立的公司Etched AI就是一家这样的公司,他们已完成1.2亿美元A轮融资,并推出全球首款Transformer专用ASIC芯片,名为“Sohu ”。

Chris Zhu(右)和Gavin Uberti

据戴伟民介绍,“Sohu ”采用台积电4nm,配有144GB HBM3E高带宽内存,其推理性能比英伟达H100快20倍,能效显著优于传统GPU。然而他最特别的地方在于把对Transformer架构的优化硬化在芯片中,不支持CNN、RNN 或 LSTM等大多数AI 架构。

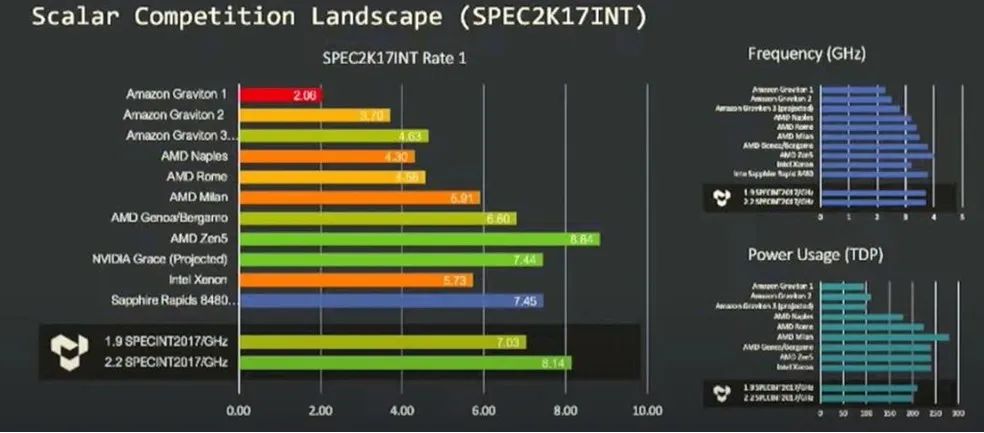

同样没有选择GPGPU路线的还有Tenstorrent。有着“硅仙人”之称的芯片大神Jim Keller在离开英特尔之后,创办了这家AI芯片公司,专门从事高性能RISC-V CPU的设计。目前该公司已经推出基于自有Ascalon处理器内核的RISC-V CPU,在衡量整数性能的SPEC CPU 2017 INT Rate基准测试中,领先于英特尔的Sapphire Rapids (7.45分) 、Nvidia的Grace (7.44分) 和 AMD的Zen 4 (6.80分) ;仅次于AMD的Zen 5 (Zen 5预计将达到8.84分,成为2024-2025年的绝对整数性能冠军)。

什么叫“Baby RISC-V”?

传统GPU的复杂控制单元占据芯片面积的40%,而“Tenstorrent最特别的地方是采用了‘Baby RISC-V’的概念,也就是用一大堆RISC-V小核心组成,而没有用GPGPU来做AI。”戴伟民指出,这种做法方案将控制单元面积大大压缩了,“那么到底什么是Baby RISC-V?”

Tenstorrent首席架构师Wei-Han Lien表示,“云端芯片为了通用性做得极其复杂,加速器则专盯一种运算。我们用大量极简 RISC-V 小核——Baby RISC-V——去控制数据流动和运算调度。它们只做‘什么时候搬数据、用什么指令’这类专精小事,面积小、功耗低、易优化,却能在大规模并行里比大核更高效。”

Tenstorrent首席架构师Wei-Han Lien

所以从定义来看,"Baby RISC-V是专为AI加速设计的极简核,每个核仅需1000逻辑门即可完成数据调度。在Blackhole芯片中,752个Baby核与16个大核协同,实现745 TOPS算力,能效比达35 TOPS/W,超越A100。" Wei-Han Lien补充道,这种小核专精设计是一种由大量小规模、专精指令核组成的架构,通过简化控制逻辑、集中硅面积优化计算单元,解决传统冯·诺依曼架构在AI负载中的“内存墙”问题,适合数据流驱动的AI加速,灵活性强,可适配从边缘侧推理到云端训练的多场景需求。

知合计算 CEO孟建熠从生态角度补充:"Baby RISC-V不是唯一路径,却是计算密集型负载的最优解之一。它把硅面积省下来堆计算单元,让‘计算’离‘业务’更近,适合重计算 Workload。”他认为,Baby RISC-V的核心价值在于解耦计算与控制。例如玄铁C930将控制通路面积减少60%,算力密度提升至128 TOPS/mm²,支持40Tops@INT8的端侧AI推理。

知合计算 CEO孟建熠

孟建熠进一步指出,RISC-V的开放性为AI芯片设计提供了统一的软件接口,既支持“Baby RISC-V”的轻量化创新,也兼容“Big RISC-V”在高性能场景的应用。RISC-V 的开放接口让不同器件都能套上同一壳,生态因此繁荣。“路径很多,大家都可以试,这是良性竞争。”

架构优化的ASIC会取代GPU吗?

谈到架构选择的问题,中兴微副总经理石义军认为需分场景看待,提醒行业不要被训练场景“一叶障目”。“训练侧关注模型能力,推理侧则适合ASIC创新,等模型收敛到少数几家,能效问题就凸显。”他指出,GPU 在优化上有很多存量工作,新架构要避开这些、把握优化时间窗和生态才能迭代。推理侧 ASIC 有很多架构创新机会,无论是端侧、边侧还是云侧推理,RISC-V 的开放性、可定制性都能提供更多选择,未来该领域创新会不断出现。

中兴微副总经理石义军

如今的RISC-V生态百花齐放,大家在你追我赶之中不知不觉繁荣了生态。国内目前体量最大的莫过于阿里巴巴达摩院的“玄铁”。作为曾在英伟达工作多年的行业老兵,阿里巴巴达摩院 RISC-副总裁 杨静 从软件生态角度切入,认为“硬件创新只是上半场,英伟达真正厉害的护城河是CUDA生态。芯片迭代慢,算法迭代快,通用 GPU+CUDA 解决了这对矛盾。RISC-V 眼下最难的是把 CUDA 生态搬过来或重建一套高效部署方式,软件栈才是长期胜负手。”

阿里巴巴达摩院 RISC-副总裁 杨静

杨静透露,达摩院“玄铁”布局已选择支持独立寄存器的方案,以适配大模型和高算力场景的需求,同时正投入重金做软件栈兼容,“把玄铁实例跑在更多框架里,让开发者无痛迁移。”

现场观众投票结果:针对AI和并行计算进行了架构优化的ASIC会取代GPU,成为未来AI训练/微调/推理芯片的发展趋势吗?(单选)

对于这个投票结果,算能高级副总裁 高鹏表示“几乎五五开,说明战局未定。AI 对算力、内存、互联的胃口远超其他应用,于是大家试数据流、存内计算、Chiplet 等新花样。”算能通过模块化指令集扩展和开源IP共享降低AI芯片设计门槛,并预测未来可能形成类似CUDA的共识性软件栈。

算能高级副总裁 高鹏

高鹏进一步指出,AI 计算对算力、存储等需求远超一般应用,RISC-V 的开放特性为相关技术创新提供载体,这是 Arm、x86 不具备的。其可扩展性和模块化能针对 AI 构建扩展指令集,实现芯片设计成本最优。而且 RISC-V 有机会挑战 CUDA 生态,其开放性和可扩展性为创新提供基础,结合国际基金会标准形成共识后,能聚集开发者。

RISC-V用在生成式AI上,有哪些优势?

从The SHD Group预测的2030年RISC-V市场份额来看,可穿戴、消费电子AI加速占比最高。戴伟民认为,除了这两个领域,AI未来能否颠覆教育和医疗也很重要,“如果要考研芯片功力,那么AI/AR眼镜会是未来智能硬件的必争之地。同时这类穿戴设备也是小模型发力的地方,由于人们对隐私的重视,穿戴设备数据一般尽量不考虑上云。”

而目前在生成式AI小模型领域,中国一骑绝尘,戴伟民举例道,微软曾定义AI PC的算力不能小于40Tops,“结果我们(中国厂商)将40TOPS直接做进了手机里(小米玄戒O1)。”

那么对于RISC-V来说,为什么 AI 是新机遇?

中国科学院计算技术研究所 副所长,中国开放指令生态(RISC-V)联盟秘书长,北京开源芯片研究院首席科学家 包云岗 认为,原因有三点:

一是能与 CPU 更好协同,从历史看浮点、多媒体指令最终都融进 CPU(如x86融合浮点单元), AI 扩展指令与 CPU 结合是趋势,利于跨模型调用;

二是灵活可定制,在推理场景需求多样时,云端要满血,边缘要蒸馏,RISC-V可在硬件层面裁剪、定制优化;

三是利于软件栈统一,今天国内各家 AI 芯片各自竖烟囱,RISC-V 通过统一扩展指令集标准,能链接全球力量构建软件栈生态(如Triton库兼容),编译器、库、框架都能共享,全球共建才有机会与 CUDA 竞争。

中国科学院计算技术研究所 副所长,中国开放指令生态(RISC-V)联盟秘书长,北京开源芯片研究院首席科学家 包云岗

现场观众投票结果:RISC-V在提升生成式AI算法的性能和效率方面,有哪些技术优势?(选三项)

未来两年内基于RISC-V的MCU、MPU率先落地的应用领域

声势浩大是一方面,落地更是厂商们重点考虑的,毕竟能持续造血才能不断迭代。

芯原股份执行副总裁、定制芯片平台事业部总经理 汪志伟 考虑到 “始终在线、超低功耗”,相关产品多为电子类,认为RISC-V选择落地领域要考虑低功耗、成本及软件成熟度。“智能家具家电(如扫地机器人)、智能手表手环、民用安防设备(带电池的智能摄像头)市场已成熟,且芯原已有客户的 RISC-V 方案落地。AI/AR/VR 眼镜等领域也在研发中,未来会很快落地。”

芯原股份执行副总裁、定制芯片平台事业部总经理 汪志伟

现场观众投票结果:针对始终在线、超低能耗、超轻量应用,未来两年内基于RISC-V的MCU、MPU率先落地的应用领域有哪些?

“现在有些RISC-V的公司很多都不盈利,还要继续融资。”戴伟民点名了一家始终保持盈利的公司——南京沁恒微电子。“我觉得你们很有希望上科创板,谈一谈沁恒微是如何在RISC-V领域始终保持盈利的?”

南京沁恒微电子技术总监、董事 杨勇 接过这个问题,表示在RISC-V浪潮里,沁恒微选择的始终是差异化的路线。“别人冲向星辰大海,我们扎在毛细血管。沁恒选择 ‘MCU+连接’垂直深耕——接口、基带、射频、Type-C 一把抓。2020 年首颗 RISC-V 芯片出来后,我们推二线调试,市场买单;再迭代单线、自适应调试,利润反哺研发,形成闭环。未来几年继续在这一亩三分地精耕细作。”

南京沁恒微电子技术总监、董事 杨勇

无独有偶,奕斯伟虽然进入RISC-V不久,但是全面开花,据悉也是处于盈利状态。谈到对于“始终在线、超低能耗、超轻量”应用领域的看法,奕斯伟计算高级副总裁、首席技术官 何宁认为,RISC-V 率先落地领域需满足三点——有新需求或需求迭代升级、能发挥其能效比及定制优化等优势、软件生态无需太多额外工作。

奕斯伟计算高级副总裁、首席技术官 何宁

曾有案例显示,奕斯伟通过RISC-V优化能效比,将钮扣电池寿命从两年延长至十年,客户直接用订单投票,奕斯伟迅速占领市场份额。何宁强调,RISC-V需要抓住“需求变化+生态适配”的窗口期,而且最好是在软件生态不需要有太多额外工作的前提下,因为软件的导入实际上比硬件更难。

RISC-V在自动驾驶的突围——开放架构如何重构车规芯片

由于近年来,从AI受益的企业大多集中在“主干”,要让更多原厂、终端企业收获AI红利,必须让这颗大树枝繁叶茂,这就涉及到“端”的问题。要说端侧,不仅仅有手机电脑、手表眼镜,汽车也是一个“端”,而且是一个最重要的“端”。

那么RISC-V在自动驾驶/ADAS的高级计算解决方案中,具备哪些优势?发展现状与前景如何?

2022年底,美国芯片初创公司Ventana Micro Systems宣布推出其 Veyron 系列高性能 RISC-V 处理器。据该团队介绍,作为当时全球性能最高的 RISC-V 处理器,该系列首款芯片Veyron V1 采用 5nm 工艺,其运行频率为 3.6GHz,可与数据中心、汽车、5G、人工智能和客户端应用的最新现有处理器相媲美。

2023年,本土RISC-V CPU IP企业芯来科技宣布,芯来NA系列CPU IP NA900获得了ISO26262最高汽车功能安全等级ASIL D的产品认证证书。这意味着NA900是全球首个获得ISO26262 ASIL-D认证的 RISC-V CPU IP产品,该产品也使得芯来科技成为全球第三家(继ARM、Synopsys后)、国内首家获得车规ISO 26262 ASIL D 产品认证的CPU IP提供商。

芯来科技创始人 胡振波

芯来科技创始人 胡振波 指出,汽车行业长期依赖私有架构导致软件生态割裂,RISC-V 作为国际标准指令集架构,可连接 “孤岛” 建立统一软件架构,且避免单一 IP 供应商依赖,依赖全产业生态,这是其在车规领域落地的最大前提。“自动驾驶和 ADAS 需强算力,对通用软件生态要求不高,RISC-V 在 AI 领域的优势可在此发挥,且其车规认证发展不错,结合软件生态、硬件算力等,在该领域有综合优势,能在多种汽车芯片应用领域落地。”

有没有RISC-V生态链EDA?

讨论最后回到了一个很实际的问题——目前有没有所谓的RISC-V EDA生态链?RISC-V工具链、验证平台的成熟度如何?和用于Arm生态的EDA工具有没有什么不同?

新思科技技术执行总监 张春林 表示,与 Arm 或 x86 相比,RISC-V 在测试集上有差距,工业界对 Arm 有完备的兼容性和 Benchmark 测试,而 RISC-V 相关测试较欠缺。另外,RISC-V 有很多定制化指令集,企业基于开源进行定制需要大量工程工作,他建议RISC-V基金会加速制定扩展指令集标准。

新思科技技术执行总监 张春林

国内EDA大厂合见工软对于RISC-V也很重视。合见工软CTO贺培鑫 认为,RISC-V 是开放架构,对其代码修改后的效果,需提前进行软硬件协同性能和功能验证,合见工软已开展相关工作,在芯片流片前预判性能与功能风险。此外,RISC-V 的开放性与芯粒结合,可通过不同组合实现不同功能,合见工软也在研发工具,帮助客户决定芯粒相关配置(如DIE工艺选择、Chiplet组合)。

合见工软CTO贺培鑫

结语

在讨论最后,戴伟民总结道:“RISC-V的生态开放性、架构定制能力与软件统一潜力,是其突破AI、汽车、低功耗等场景的关键,但生态链成熟度仍是短板。企业通过差异化路径(如Tenstorrent的"Baby RISC-V"、沁恒的垂直深耕)推动技术落地,同时需补足工具链与测试集短板以加速生态成熟。未来需通过标准化、开源IP共享和软件栈统一,构建类似CUDA的生态,实现与Arm、x86及CUDA的长期博弈。”

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊