真不是为了钱!三星顶尖人才集体跑路 SK 海力士

- 2025-07-29 11:30:00

关注我们 设为星标

EETOP

百万芯片工程师专业技术论坛

官方微信号

报名邀请:Cadence中国用户大会——定制模拟设计、系统验证、AI 驱动验证专题

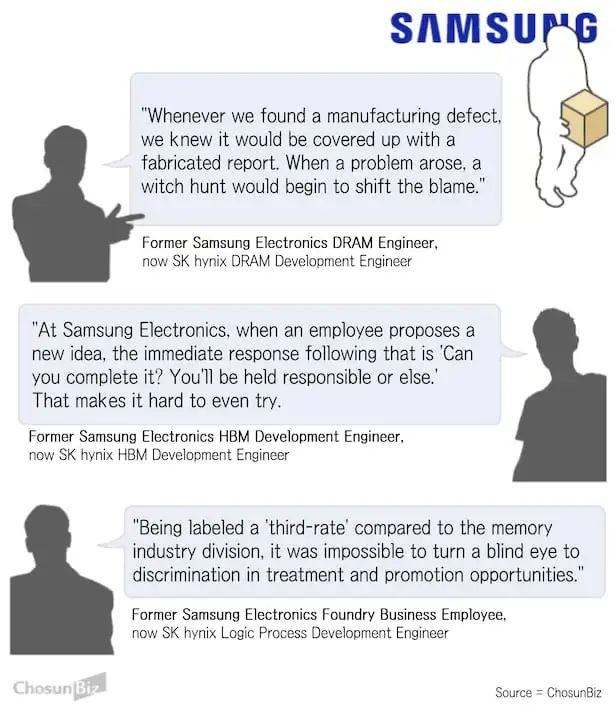

在三星电子负责 DRAM(动态随机存取存储器 )工艺长达十年后,一位 43 岁、化名 A 的工程师于 2023 年入职 SK 海力士。最令他惊讶的并非技术工作本身,而是摆脱了他口中 “虚假汇报文化” 后的解脱。在三星,跨部门项目常常会暴露出工艺或设计上的缺陷,但为了避免内部追责,这些问题通常会被轻描淡写地带过。“所有人都清楚这种‘游戏规则’,” 他表示,“把问题最小化,否则你的团队就会‘遭殃’。”

工程师 B 毕业于顶尖工程院校后加入三星,在该公司工作了八年,也表达了类似的看法。他原本以为韩国领先的芯片制造商之间不会有太大差异,却发现 SK 海力士的运作模式截然不同:自下而上的决策机制以及公开的内部竞争。“在三星,对于任何新提议,第一反应往往是‘如果失败了,你能承担责任吗?’” 他说道,“仅这一点就扼杀了创新。”

随着三星在存储芯片领域的主导地位逐渐削弱—— 尤其是在高带宽内存(HBM )和 DRAM 方面 —— 行业分析师指出,顶尖工程人才的流失正在加速一场更深层次的危机。C 今年 51 岁,在三星设计 DRAM 工艺近 20 年,如今在 SK 海力士领导第六代(1c )10 纳米级 DRAM 的开发工作。他表示,近年来从三星跳槽到 SK 海力士的情况大幅增加。“这不仅仅是薪资的问题,” 他说,“而是僵化的层级制度、表面功夫式的职场政治,以及抑制冒险精神的人力资源体系。”

在争夺人工智能时代存储芯片主导权的竞赛中,这种内部创新的退缩愈发明显。据 B 介绍,SK 海力士鼓励不同团队之间就竞争性封装技术(如 MR - MUF 和混合键合技术 )展开竞争,然后根据性能和成本进行筛选。而在三星,他表示,首要考虑的是如果出现问题,谁会被追责。

这背后的利害关系重大。SK 海力士的内部竞争已经带来了突破:工程师们曾认为 MR - MUF 技术无法扩展到 16 层以上。但通过内部反复迭代,该公司将其扩展到了 20 层,大幅提升了效率。B 将这种做法与台积电的做法相提并论:“把现有工具用到极致,以降低成本并在性能上领先。”

相比之下,三星仍存在规避风险的心态。“当第一个问题是‘你能保证这会成功吗?’时,新想法就会戛然而止。”B 说道。

如今,人才外流已不仅仅局限于存储芯片领域。随着下一代 HBM4 整合逻辑芯片(这需要先进的晶圆代工工艺 ),SK 海力士已开始招募三星的 FinFET(鳍式场效应晶体管 )工程师。自 2024 年以来,已有小团队陆续跳槽,每次有两到三人。

43 岁的前晶圆代工工程师 D 提到,长期亏损、产能利用率低以及对业务分拆的猜测是他离职的原因。他还指出,三星备受推崇的存储部门与其晶圆代工业务之间存在士气差距。

现就职于 SK 海力士的高级研究员 E 则把矛头指向三星的 “血统心态”。“除非你是通过公司内部体系一步步升上来的,否则几乎不可能进入存储部门的领导层。” 他表示。

相反,SK 海力士不论资历,只看业绩,不仅任用从三星跳槽过来的资深人士,还让不太知名的软件专业人士担任关键岗位。这种开放态度已见成效。曾经在 NAND 闪存技术方面落后的 SK 海力士,如今已缩小了差距。其近期推出的高利润率产品,性能已达到或超过三星和美光的同类产品。

关键招聘起到了重要作用。崔正达尔(音译)曾在 SK 海力士领导开发出全球首款 321 层 NAND 闪存,他此前是三星的高管,还曾获得三星的 “三星骄傲奖”。他的前任郑泰成(音译)在加入 SK 海力士之前,也在三星工作了二十年。

专家表示,三星的问题并非出在技术上,而是结构上。“这是一个‘管理优先’的组织,” 西江大学商学院教授金永珍(音译)表示,“工程决策要经过财务指标的筛选。如果领导层不重置这套体系,三星的半导体优势可能会继续被削弱。”

欢迎加入 EETOP 微信群

CadenceLIVE China 2025 中国用户大会

邀请报名

AI驱动验证专题

扫码添加微信

扫码添加微信

- 点赞 (0)

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊