时序优化--从寄存器摆放位置入手

- 2025-07-21 09:44:07

IC设计中,因为逻辑功能的要求,有些关键路径不能通过插入Pipeline的方式优化时序,又因为性能的要求也不能粗暴地降低时钟频率。此时可以从关键寄存器的摆放位置角度考虑实现时序优化。通过对非关键路径插入Pipeline从而减少对关键寄存器的时序约束,让关键寄存器能够灵活摆放,减少路径延时从而达到优化关键路径的目的。

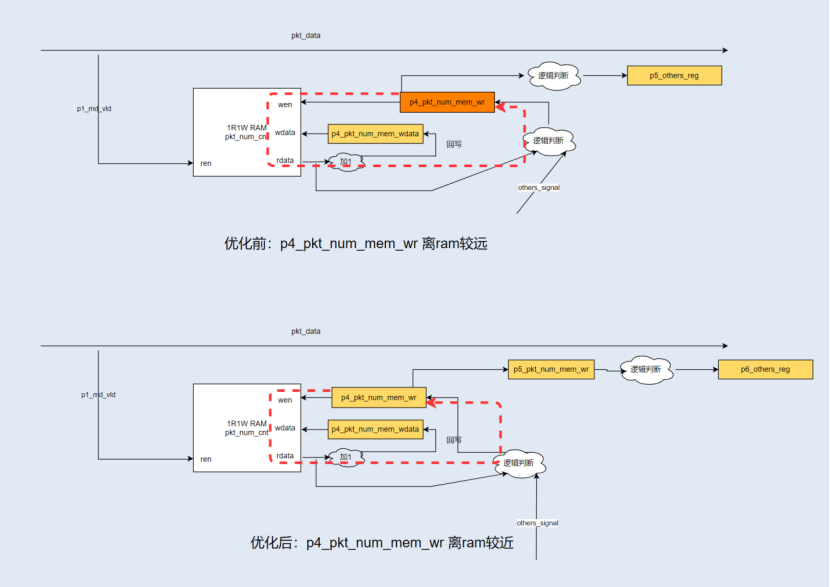

如图所示,图中的1R1W的RAM作为有效包数量统计的RAM,当有数据包来临时p1_md_vld为1,从RAM读数据,经过2拍延时后得到了读数据,读数据加1得到打一拍得到p4_pkt_num_mem_wdata,同时mem写信号p4_pkt_num_mem_wr需要根据读数据和其他信号进行逻辑判断后才能得到,因为需要支持背靠背统计累加,因此RAM的mem写信号wen到读数据rdata之间存在组合逻辑,在本案例中关键路径是红色虚线表示的路径:p4_pkt_num_mem_wr->mem的rdata->逻辑判断->p4_pkt_num_mem_wr。

在优化前,p4_pkt_num_mem_wr因为p5_others_reg寄存器的时序要求而离ram比较远,此时路径延时较长。优化方法:将寄存器p4_pkt_num_mem_wr打一拍得到p5_pkt_num_mem_wr再通过逻辑判断得到寄存器p6_others_reg。因为p4_pkt_num_mem_wr和p5_pkt_num_mem_wr没有复杂逻辑因此此时p4_pkt_num_mem_wr摆放位置可以离RAM更近一些。

此方法的优化效果在不同的代码中存在明显差异。如果关键寄存器p4_pkt_num_mem_wr驱动的逻辑特别多,即在优化前的图中,p5_others_reg数量越多,其逻辑判断越复杂,则此方法的效果则越好。在FPGA设计中,资源利用率较高时,此方法的优化效果更加明显。

扫码添加微信

扫码添加微信

- 点赞 0

-

分享

微信扫一扫

-

加入群聊

扫码加入群聊

扫码加入群聊